Frequency Deputy Unit

User Manual

Version 002

Innovation with Integrity

NMR

#### Copyright © by Bruker Corporation

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or by any means without the prior consent of the publisher. Product names used are trademarks or registered trademarks of their respective holders.

This manual was written by

Willy Uhrig and Thomas Eckert

© August 16, 2013: Bruker Corporation

Rheinstetten, Germany

P/N: Z31976

#### DWG-Nr.: Z4D11450A

For further technical assistance on the FRED unit, please do not hesitate to contact your nearest BRUKER dealer or contact us directly at:

> BRUKER Corporation am Silberstreifen D-76287 Rheinstetten Germany

Phone:

+ 49 721 5161 0

FAX:

+ 49 721 5171 01

E-mail:

nmr-support@bruker.de

Internet:

www.bruker.com

| 1 | Abou                                                                                      | t                                                                                                                                                                                                                                                                                              | 5                                                                                |

|---|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|   | 1.1                                                                                       | This Manual                                                                                                                                                                                                                                                                                    | 5                                                                                |

|   | 1.2                                                                                       | Policy Statement                                                                                                                                                                                                                                                                               | 5                                                                                |

|   | 1.3                                                                                       | Symbols and Conventions                                                                                                                                                                                                                                                                        | 5                                                                                |

| 2 | Introc                                                                                    | luction                                                                                                                                                                                                                                                                                        |                                                                                  |

|   | 2.1                                                                                       | Concept                                                                                                                                                                                                                                                                                        |                                                                                  |

|   | 2.2                                                                                       | Limitations of Liability                                                                                                                                                                                                                                                                       |                                                                                  |

|   | 2.3                                                                                       | Spare Parts                                                                                                                                                                                                                                                                                    |                                                                                  |

|   | 2.4                                                                                       | Warranty Terms                                                                                                                                                                                                                                                                                 |                                                                                  |

|   | 2.5                                                                                       | Customer Service                                                                                                                                                                                                                                                                               | 8                                                                                |

| 3 |                                                                                           | y                                                                                                                                                                                                                                                                                              |                                                                                  |

|   | 3.1                                                                                       | Intended Use                                                                                                                                                                                                                                                                                   |                                                                                  |

|   | 3.2                                                                                       | General Safety Instructions                                                                                                                                                                                                                                                                    | 9                                                                                |

| 4 | Techr                                                                                     | nical Data                                                                                                                                                                                                                                                                                     | 11                                                                               |

|   | 4.1                                                                                       | General Information                                                                                                                                                                                                                                                                            | 11                                                                               |

|   | 4.2                                                                                       | Utility Requirements                                                                                                                                                                                                                                                                           | 11                                                                               |

|   | 4.3                                                                                       | Operating Conditions                                                                                                                                                                                                                                                                           | 12                                                                               |

|   | 4.3.1                                                                                     | Operating Environment                                                                                                                                                                                                                                                                          | 12                                                                               |

|   | 4.4                                                                                       | Rating Plates                                                                                                                                                                                                                                                                                  | 12                                                                               |

| 5 | Desig                                                                                     | In and Function                                                                                                                                                                                                                                                                                | 13                                                                               |

|   | 5.1                                                                                       | Product and Manufacturer                                                                                                                                                                                                                                                                       | 13                                                                               |

|   | 5.2                                                                                       | General Description                                                                                                                                                                                                                                                                            | 10                                                                               |

|   |                                                                                           |                                                                                                                                                                                                                                                                                                | 13                                                                               |

|   | 5.3                                                                                       | Features                                                                                                                                                                                                                                                                                       |                                                                                  |

|   | 5.3<br>5.4                                                                                |                                                                                                                                                                                                                                                                                                | 15                                                                               |

|   |                                                                                           | Features                                                                                                                                                                                                                                                                                       | 15<br>15                                                                         |

|   | 5.4                                                                                       | Features<br>Functional Description<br>The PCI Interface<br>PCI Software Interface                                                                                                                                                                                                              | 15<br>15<br>15<br>16                                                             |

|   | 5.4<br>5.4.1<br>5.4.2<br>5.4.3                                                            | Features<br>Functional Description<br>The PCI Interface                                                                                                                                                                                                                                        | 15<br>15<br>15<br>16                                                             |

|   | 5.4<br>5.4.1<br>5.4.2                                                                     | Features<br>Functional Description<br>The PCI Interface<br>PCI Software Interface                                                                                                                                                                                                              | 15<br>15<br>15<br>16<br>20                                                       |

|   | 5.4<br>5.4.1<br>5.4.2<br>5.4.3                                                            | Features<br>Functional Description<br>The PCI Interface<br>PCI Software Interface<br>BIS Flash Prom at the Local Bus<br>Register and Device Code Description<br>LVDS Word Structure                                                                                                            | 15<br>15<br>15<br>16<br>20<br>23<br>29                                           |

|   | 5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.5<br>5.6<br>5.7                                       | Features<br>Functional Description<br>The PCI Interface<br>PCI Software Interface<br>BIS Flash Prom at the Local Bus<br>Register and Device Code Description<br>LVDS Word Structure<br>The FRED Board H12607                                                                                   | 15<br>15<br>15<br>16<br>20<br>23<br>29<br>32                                     |

|   | 5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.5<br>5.6<br>5.7<br>5.8                                | Features<br>Functional Description<br>The PCI Interface<br>PCI Software Interface<br>BIS Flash Prom at the Local Bus<br>Register and Device Code Description<br>LVDS Word Structure<br>The FRED Board H12607<br>JTAG Structure                                                                 | 15<br>15<br>15<br>16<br>20<br>23<br>29<br>32<br>32                               |

|   | 5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                         | Features<br>Functional Description<br>The PCI Interface<br>PCI Software Interface<br>BIS Flash Prom at the Local Bus<br>Register and Device Code Description<br>LVDS Word Structure<br>The FRED Board H12607<br>JTAG Structure<br>Power Requirements                                           | 15<br>15<br>16<br>20<br>23<br>29<br>32<br>32<br>34                               |

|   | 5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.5<br>5.6<br>5.7<br>5.8                                | Features<br>Functional Description<br>The PCI Interface<br>PCI Software Interface<br>BIS Flash Prom at the Local Bus<br>Register and Device Code Description<br>LVDS Word Structure<br>The FRED Board H12607<br>JTAG Structure                                                                 | 15<br>15<br>16<br>20<br>23<br>29<br>32<br>32<br>34                               |

| 6 | 5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                 | Features<br>Functional Description<br>The PCI Interface<br>PCI Software Interface<br>BIS Flash Prom at the Local Bus<br>Register and Device Code Description<br>LVDS Word Structure<br>The FRED Board H12607<br>JTAG Structure<br>Power Requirements                                           | 15<br>15<br>16<br>20<br>23<br>29<br>32<br>32<br>34<br>34                         |

| 6 | 5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                 | Features<br>Functional Description<br>The PCI Interface<br>PCI Software Interface<br>BIS Flash Prom at the Local Bus<br>Register and Device Code Description<br>LVDS Word Structure<br>The FRED Board H12607<br>JTAG Structure<br>Power Requirements<br>Pin Allocation for the LVDS Connectors | 15<br>15<br>16<br>20<br>23<br>29<br>32<br>32<br>34<br>34                         |

| 6 | 5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br><b>Trans</b> | Features<br>Functional Description<br>The PCI Interface<br>PCI Software Interface<br>BIS Flash Prom at the Local Bus<br>Register and Device Code Description<br>LVDS Word Structure<br>The FRED Board H12607<br>JTAG Structure<br>Power Requirements<br>Pin Allocation for the LVDS Connectors | 15<br>15<br>16<br>20<br>23<br>29<br>32<br>32<br>32<br>34<br>34<br>34<br>37<br>37 |

|     | 6.3      | Storage                          |    |

|-----|----------|----------------------------------|----|

| 7   | Instal   | lation and Initial Commissioning |    |

| -   | 7.1      | Safety                           |    |

|     | 7.2      | Installation                     |    |

|     | 7.2.1    | Console Installation             |    |

|     | 7.2.2    | External Connections             |    |

| 8   | Opera    | ating Instructions               | 43 |

|     | 8.1      | Switching ON the FRED Unit       |    |

|     | 8.2      | Switching OFF the FRED Unit      |    |

|     | 8.3      | Operation                        | 43 |

|     | 8.4      | Operator Protection              | 44 |

|     | 8.5      | Unit Protection                  |    |

|     | 8.5.1    | Incorrect Cable Connections      | 45 |

| 9   | Maint    | enance and Cleaning              | 47 |

|     | 9.1      | Safety                           |    |

|     | 9.1.1    | Environmental Protection         |    |

|     | 9.2      | Maintenance                      |    |

|     | 9.3      | Cleaning                         |    |

|     | 9.4      | Service Requests                 |    |

| 10  | Disma    | antling and Disposal             |    |

| 11  | Conta    | act                              | 51 |

| ••  | Come     |                                  |    |

| App | bendix / | Α                                | 53 |

|     | A.1      | Warning Signs                    | 53 |

|     | A.2      | Figures                          |    |

|     | A.3      | Tables                           | 57 |

|     | A.4      | Glossary                         |    |

|     | A.5      | Index                            | 61 |

# 1 About

## 1.1 This Manual

This manual enables safe and efficient handling of the device.

This manual is an integral part of the device, and must be kept in close proximity to the device where it is permanently accessible to personnel.

Before starting any work, the personnel must have read the manual thoroughly and understood its contents. Compliance with all specified safety instructions and operating instructions is vital to ensure safe operation.

In addition, local accident prevention regulations and general safety instructions must be observed for the operational area of the device.

Illustrations in this manual are intended to facilitate basic understanding, and may differ from the actual design.

In addition to the user manual, instructions concerning local labor protection laws, operator regulations, and tools and supplies must be available and adhered to.

## **1.2 Policy Statement**

It is the policy of Bruker to improve products as new techniques and components become available. Bruker reserves the right to change specifications at any time.

Every effort has been made to avoid errors in text and figure presentation in this publication. In order to produce useful and appropriate documentation, we welcome your comments on this publication. Support engineers are advised to regularly check with Bruker for updated information.

Bruker is committed to providing customers with inventive, high quality products and services that are environmentally sound.

## 1.3 Symbols and Conventions

Safety instructions in this manual are marked with symbols. The safety instructions are introduced using indicative words which express the extent of the hazard.

In order to avoid accidents, personal injury or damage to property, always observe safety instructions and proceed with care.

##

This combination of symbol and signal word indicates an immediately hazardous situation which could result in death or serious injury unless avoided.

## **A**WARNING

This combination of symbol and signal word indicates a potentially hazardous situation which could result in death or serious injury unless avoided.

# **A**CAUTION

This combination of symbol and signal word indicates a possibly hazardous situation which could result in minor or slight injury unless avoided.

NOTICE

This combination of symbol and signal word indicates a possibly hazardous situation which could result in damage to property or the environment unless avoided.

**1** This symbol highlights useful tips and recommendations as well as information designed to ensure efficient and smooth operation.

#### **Special Safety Instructions**

The following symbols are used in the safety instructions to draw attention to specific danger:

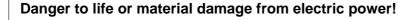

#

This combination of symbol and signal word indicates dangers posed by electric power. If the safety instructions are not observed, there is a danger of serious or fatal injuries.

**2** Introduction

The Frequency Deputy (FRED) unit is used in MRI **AVANCE III** spectrometers to receive frequency and phase information from frequency offset devices, and integrate phase and frequency offset commands into the data flow from Frequency Controllers (FCTRL) to Signal Generation Units (SGU).

## 2.1 Concept

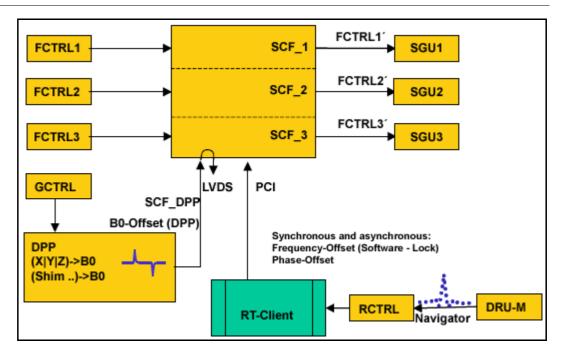

The FRED unit receives frequency and phase information from frequency offset devices (B0 term of cross-preemphasis from the DPP and the software lock from the RT-client) and integrates phase and frequency offset commands into the data flow of from 1 to 3 FCTRL's to 1, 2 or 3 SGU's respectively.

The FRED calculates a global frequency and phase offset from the B0 data coming from the DPP, via the LVDS, and from values coming from the RT-Client via PCI. The result is then scaled according to the scaling factors (SCF\_1, SCF\_2 and SCF\_3) for each frequency channel, then the frequency or phase offset values are transferred to the connected SGU(s).

Special MRI applications use the FRED unit to correct the offset of the spectrometer B0 field by switching the frequency offset at the SGU.

Refer to "Design and Function" on page 13 for more information.

Figure 2.1 The Frequency Deputy Unit

### 2.2 Limitations of Liability

All specifications and instructions in this manual have been compiled taking account of applicable standards and regulations, the current state of technology and the experience and insights we have gained over the years.

The manufacturer accepts no liability for damage due to:

- Failure to observe this manual.

- Improper use.

- Deployment of untrained personnel.

- Unauthorized modifications.

- Technical modifications.

- Use of unauthorized spare parts.

The actual scope of supply may differ from the explanations and depictions in this manual in the case of special designs, take-up of additional ordering options, or as a result of the latest technical modifications.

The undertakings agreed in the supply contract as well as the manufacturer's Terms and Conditions, Terms of Delivery, and the legal regulations applicable at the time of conclusion of the contract shall apply.

## 2.3 Spare Parts

Spare parts may be obtained from authorized dealers or directly from the manufacturer. See "Contact" on page 51 for the address.

## 2.4 Warranty Terms

The warranty terms are included in the manufacturer's Terms and Conditions.

## 2.5 Customer Service

Our customer service division is available to provide technical information. See for "Contact" on page 51 contact details.

In addition, our employees are always interested in acquiring new information and experience gained from practical applications; such information and experience may help improve our products.

# 3 Safety

This chapter provides an overview of all the main safety aspects involved in ensuring optimal personnel protection and safe and smooth operation.

Non-compliance with the action guidelines and safety instructions contained in this manual may result in serious hazards. Before starting any work, personnel must read this chapter thoroughly and understand its contents.

## 3.1 Intended Use

The unit has been designed and constructed solely for the intended use described here.

The FRED units must only be used for the limited purpose of controlling the spectrometer B0 field by switching the frequency and phase offset of the SGU in Bruker AVANCE III spectrometers.

Intended use also includes compliance with all specifications in this manual.

Any use which exceeds or differs from the intended use shall be considered improper use.

No claims of any kind for damage will be entertained if such claims result from improper use.

## 3.2 General Safety Instructions

The FRED can be damaged by inappropriate usage. In this case the equipment must not be used until it has been checked by service personnel.

The user should re-check the equipment at regular intervals for any damage or wear and is expected to inform the service immediately of any abnormality.

Do not operate the equipment in the presence of flammable gases or fumes.

##

Material or personnel damage from worn or damaged parts.

Damaged or worn parts may result if one or the following circumstances occurs:

- ► The power cord, power plug or power supply are cracked, brittle or damaged.

- ► Signs of excessive heat appear.

- ▶ There is evidence or suspicion that a liquid has intruded into any enclosure.

- ► The power cord or the power supply have been in contact with any liquid.

- ▶ The FRED has been dropped or damaged in any way.

- The equipment does not work correctly

In the unlikely event one of the above occurs:

- ► Stop using the equipment.

- Disconnect the power supply.

- Inform service and ask for instructions.

- **1** Only trained service personnel are allowed to mount, retrofit, repair, adjust and dismantle the FRED unit. Do not try to service the equipment unless you are specifically asked to do so and are given instructions by the service staff. In case of questions or problems, please contact your nearest Bruker office or representative.

- **1** Before maintenance, repair or shipment, the FRED unit must be completely disconnected from the power supply and dismounted from its rack.

# 4 Technical Data

## 4.1 General Information

| Specification | Value | Unit |

|---------------|-------|------|

| Weight        | 2.5   | kg   |

| Length        | 46.2  | cm   |

| Width         | 29.0  | cm   |

| Height        | 4.3   | cm   |

Table 4.1 Technical Data: General Information

## 4.2 Utility Requirements

| Ingress Protection<br>Class:         | IP 20, secured against touching dangerous points inside, not secured against ingress of water.                                                                               |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Over-voltage Protection<br>Category: | CAT II, according to EN61010–1or IEC60664–1 safe against over-voltage by switching, not safe against lightning. Surge immunity of PSU is level 3, according to IEC61000–4–5. |

| IEC Protection Class:                | Class I, according the IEC 61140, connected to mains by phase, neutral and protective earth.                                                                                 |

| Input Voltage Range:                 | 208 V to 230 V.                                                                                                                                                              |

| Frequency:                           | 50/60 Hz.                                                                                                                                                                    |

| Input Power:                         | 30 VA.                                                                                                                                                                       |

| Fuse On Mains Input:                 | 250 VAC 2 A.                                                                                                                                                                 |

| Connection:                          | Socket outlet with phase, neutral and protective-earth according to VDE 0620-1.                                                                                              |

Table 4.2 Technical Data: Utility Requirements

## 4.3 **Operating Conditions**

#### 4.3.1 Operating Environment

| Permissible ambient temperature: | 5°C to 40°C.                                                                                                                              |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Permissible altitude:            | Up to 2000 meters above sea level.                                                                                                        |

| Relative humidity:               | Maximum of 80% for temperatures up to 31°C, linearly decreasing to 50% at a temperature of 40°C.                                          |

| Permissible storage temperature: | 5°C to 40°C.                                                                                                                              |

| Pollution degree:                | The acceptable pollution degree is 2. According to EN 61010-1 or IEC 60664-1. Any pollution is non-conductive, except condensed moisture. |

Table 4.3 Operating Environment

## 4.4 Rating Plates

The rating plate is located at the power input and includes the following information:

- Manufacturer

- Type

- Voltage

- Frequency

- Apparent power consumption, maximum

- PN: Part Number

- SN: Serial Number

- Va: Variant

- ECL: Engineering Change Level

# **5** Design and Function

## 5.1 Product and Manufacturer

| Product:      | FRED Unit P<br>FRED Board<br>Power Supply<br>LVDS Cable<br>PCI Express | P/N H1260<br>y P/N 88873<br>1m P/N 868 | 7<br>3<br>68                                                                                                                      |

|---------------|------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Manufacturer: | Bruker BioSp<br>Silberstreifen<br>76287 Rheins<br>Germany              | 4                                      |                                                                                                                                   |

| Conformity:   | EN 61010-1                                                             | 2010-06                                | Safety requirements for electrical<br>equipment for measurement, control,<br>and laboratory use - Part 1: General<br>requirements |

### 5.2 General Description

The Frequency Deputy (FRED) is a device that receives frequency and phase information from frequency offset devices (B0 term of cross-preemphasis from the DPP and software lock from RT-client) and integrates phase and frequency offset commands into the data flow of 1 to 3 FCTRL's to 1, 2 or 3 SGU's respectively.

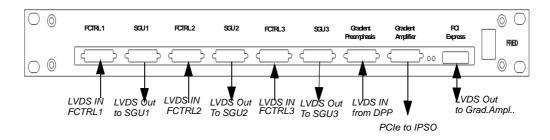

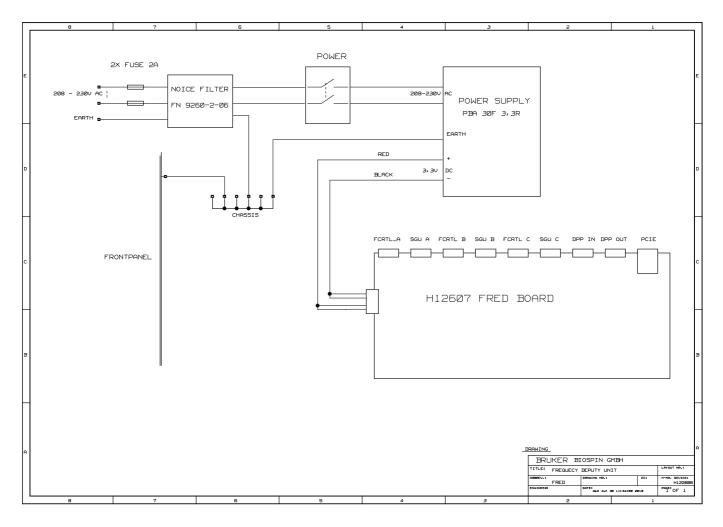

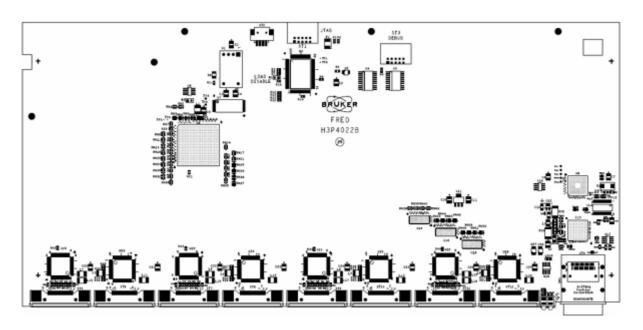

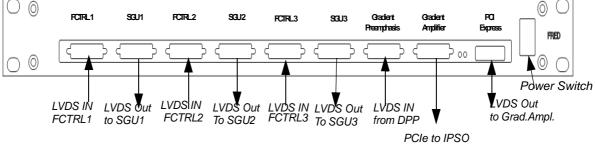

The FRED board is integrated in a 1HE 19" chassis which includes the power supply. On the front of the chassis are the connector pairs for the three FCTRL to SGU LVDS channels (IN/OUT), the LVDS IN/OUT from the DPP to the gradient amplifier, and the PCIe port to the IPSO unit. The unit can be turned on using the power switch on the front of the chassis. The power state is indicated by an indicator light. An indicator light also indicates that the PCI link is functioning.

The FRED unit is a part of the IPSO AQS system and is installed in the same AQS rack.

#### Figure 5.1 Front View of the External Connections

The FRED calculates a global frequency and phase offset from B0 data, coming from the DPP via the LVDS, and from values coming from the RT-Client via the PCI bus. The result is then scaled according to the scaling factors (SCF\_1, SCF\_2 and SCF\_3) for each frequency channel prior to transferring frequency or phase offset values to the connected SGU(s). A scaling factor with a value 0 disables the corresponding channel for B0 offset correction. Frequency and phase offset values are only embedded in the FCTRL to SGU data path if a new offset values is activated. The LVDS inputs are all checked for parity error. In case of a parity error an interrupt to the RT-client is generated.

All register and RAM buffers must be initialized before the start of the experiment.

Special MRI applications use the FRED unit to correct the offset of spectrometer B0 field by switching the frequency offset at the SGU.

Figure 5.2 The FRED Unit Wiring

### 5.3 Features

- A 48-bit LVDS interface to connect the FCTRL, DPP and SGU.

- PCI express generation 1 interface to connect the RT-client (IPSO host) via cable.

- Simultaneous frequency (B0) and phase offset control of up to 3 channels at 80 MHz speed.

- Pulse program controlled synchronous update of the frequency and phase offsets from DPP.

- Asynchronous frequency and phase offset switching via PCIe bus (RT-Client).

- Programmable delay register to adjust the update of the B0 offset to the gradient switching time.

- JTAG test and programming interface.

## 5.4 Functional Description

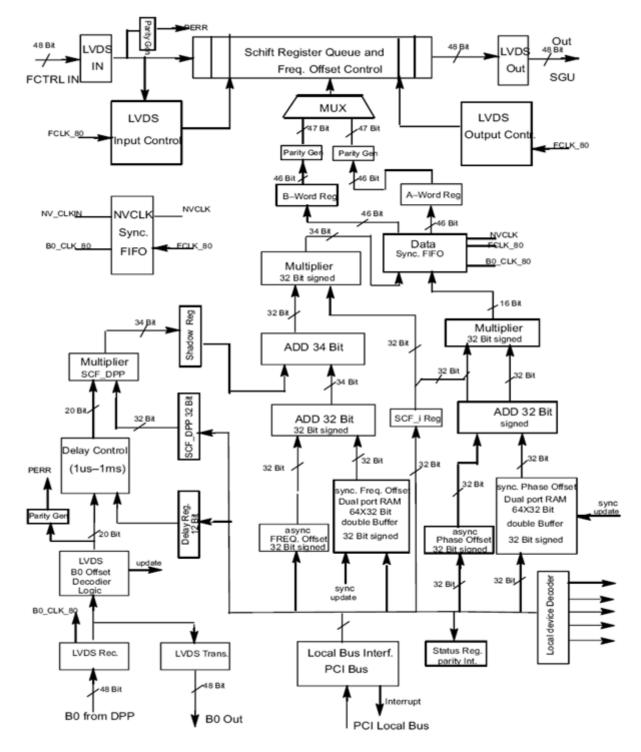

Figure 5.3 Block Diagram for the FRED

#### 5.4.1 The PCI Interface

The PCI interface for the FRED is implemented by the PCIe to PCI bridge (PEX 8112 controller) and the PCI to local bus controller (PCI9030 PLX Technologies) to translate the PCI bus to the local bus.

The PCI 9030 controller translates external PCI accesses to internal local bus accesses and vice versa.

The local bus for the controller is connected to the FPGA to access the various registers inside the chip. To communicate with the FPGA over the PCIe Interface, the 80 MHz clock signal must be provided at the LVDS Input "Gradient Pre-emphasis" from the DPP. The PCI controller "PCI 9030" from "PLX Technology" provides the interface between the PCI bus and the internal local bus to the FPGA. The controller configures itself after a reset or power-up by reading the content of a dedicated serial EEPROM. Some values of the configuration registers are read directly out of the PROM and some are generated from the PROM content.

The address map for this EEPROM and its contents are listed below.

The EEPROM of the PCI 9030 controller is programmed using the CASCON JTAG software.

#### 5.4.2 PCI Software Interface

The PCI address map of the internal FRED addresses at the local bus is built by the BIOS after power-up using the contents in the configuration registers "Base address 0...5". The results are the PCI base addresses of the local bus chip selects, which are written by the BIOS in the same configuration registers.

| EEPROM<br>Offset | Register<br>Offset<br>Configura-<br>tion Space<br>Address | Register Description                                 | Affected Bits                 | Regis-<br>ter<br>Values | Value Descrip-<br>tion |

|------------------|-----------------------------------------------------------|------------------------------------------------------|-------------------------------|-------------------------|------------------------|

| 00 h             | 02                                                        | Device ID                                            | PCIDR[31:16]                  | 9030 h                  |                        |

| 02 h             | 00 h                                                      | Vendor ID                                            | PCIIDR [15:0]                 | 10B5 h                  |                        |

| 04 h             | 06 h                                                      | PCI Status                                           | PCISR [15:0]                  | 0290 h                  |                        |

| 06 h             | 04 h                                                      | PCI Command                                          |                               | 0000 h                  | Reserved               |

| 08 h             | 0A h                                                      | Class Code                                           | PCICCR [15:8]                 | 0680 h                  |                        |

| 0A h             | 08 h                                                      | Class Code / Revision                                | PCICCR [7:0/<br>PCIREV [7:0]  | 000A h                  |                        |

| 0C h             | 2E h                                                      | Subsystem ID                                         | PCISID [15:0]                 | 0300 h                  |                        |

| 0E h             | 2C h                                                      | Subsystem Vendor ID                                  | PCIVSID [15:0]                | 0000 h                  |                        |

| 10 h             | 36 h                                                      | MSB New Capability Pointer                           |                               | 0000 h                  | Reserved               |

| 12 h             | 34 h                                                      | LSB New Capability Pointer                           | CAP_PTR[7:0]                  | 0040 h                  |                        |

| 14 h             | 3E h                                                      | Maximum Latency & mini-<br>mum Grant can't be loaded |                               | 0000 h                  | Reserved               |

| 16 h             | 3C h                                                      | Interrupt Pin                                        | PCIIPR [7:0]/<br>PCIILR [7:0] | 01FF h                  |                        |

| 18 h             | 42 h                                                      | MSW of Power Management<br>Capabilities              | PMC[15:11, 5, 3:0]            | 4801 h                  |                        |

| 1    |      |                                                               |                                 |        |                                                   |

|------|------|---------------------------------------------------------------|---------------------------------|--------|---------------------------------------------------|

| 1A h | 40 h | LSW of Power Management<br>Next Capability pointer            | PMNEXT [7:0] /<br>PMCCAPID[7:0] | 4801 h |                                                   |

| 1C h | 46 h | MSW of Power Management<br>data                               |                                 | 0000 h | Reserved                                          |

| 1E h | 44 h | LSW of Power Management<br>Control / Status                   | PMCSR [14:8]/<br>PCIILR [7:0]   | 0000 h |                                                   |

| 20 h | 4A h | MSW of Hot Swap/Control                                       |                                 | 0000 h | Reserved                                          |

| 22 h | 48 h | LSW of Hot Swap Next<br>Capability Pointer / Control          | HS_NEXT[7:0]/<br>HS_CNTL[7:0]   | 4C06   |                                                   |

| 24 h | 4E h | PCI Vital Product Data<br>Address                             |                                 | 0000 h | Reserved                                          |

| 26 h | 4C h | PCI Vital Product Data Next<br>Capability Pointer/Control     | PVPD_NEXT[7:0]<br>PVPDCNTL[7:0] | 0003 h |                                                   |

|      |      | Content of Loca                                               | al Register                     |        |                                                   |

| 28 h | 02 h | MSW of Local Address<br>Space 0 Range                         | LAS0RR[31:16]                   | 0FFF h | 2 KB Local<br>Address Space                       |

| 2A h | 00   | LSW of Local Address<br>Space 0 Range                         | LASORR[15:0]                    | F000 h | non-prefetch<br>FPGA Dev.                         |

| 2C h | 06 h | MSW of Local Address<br>Space 1 Range                         | LAS1RR[31:16]                   | 0FF0 h | 1 MB Local<br>Address Space                       |

| 2E h | 04 h | LSW of Local Address<br>Space 1 Range                         | LAS1RR[15:0]                    | 0000 h | <ul> <li>unused</li> <li>default value</li> </ul> |

| 30 h | 0A h | MSW of Local Address<br>Space 2 Range                         | LAS1RR[31:16]                   | 0FF0 h | 1 MB Local<br>Address Space                       |

| 32 h | 08 h | LSW of Local Address<br>Space 2 Range                         | LAS1RR[15:0]                    | 0000 h | unused<br>default value                           |

| 34 h | 0E h | MSW of Local Address<br>Space 3 Range                         | LAS1RR[31:16]                   | 0FF0 h | 64 KB Local<br>Address Space                      |

| 36 h | 0C h | LSW of Local Address<br>Space 3 Range                         | LAS1RR[15:0]                    | 0000 h | non-prefetch<br>BIS FLASH                         |

| 38 h | 12 h | MSW of Expansion ROM<br>Range                                 | EROMRR[31:16]                   | 0000 h | Disable                                           |

| 3A h | 10 h | LSW of Expansion ROM<br>Range                                 | EROMRR[15:0]                    | 0000 h |                                                   |

| 3C h | 16 h | MSW of Local Address<br>Space 0 Local Base Address<br>(Remap) | LAS0BA[31:16]                   | 0001 h | enable CE 0                                       |

| 3E h | 14 h | LSW of Local Address<br>Space 0 Local Base Address<br>(Remap) | LAS0BA[15:0]                    | 0001 h |                                                   |

| [    |      |                                                                              |                | 1      | <del>,                                    </del> |

|------|------|------------------------------------------------------------------------------|----------------|--------|--------------------------------------------------|

| 40 h | 1A h | MSW of Local Address<br>Space 1 Local Base Address<br>(Remap)                | LAS1BA[31:16]  | 0000 h | enable CE 1                                      |

| 42 h | 18 h | LSW of Local Address<br>Space 1 Local Base Address<br>(Remap)                | LAS1BA[15:0]   | 0000 h |                                                  |

| 44 h | 1E h | MSW of Local Address<br>Space 2 Local Base Address<br>(Remap)                | LAS2BA[31:16]  | 0000 h | enable CE 2                                      |

| 46 h | 1C h | LSW of Local Address<br>Space 2 Local Base Address<br>(Remap)                | LAS2BA[15:0]   | 0000 h |                                                  |

| 48 h | 22 h | MSW of Local Address<br>Space 3<br>Local Base Address<br>(Remap)             | LAS3BA[31:16]  | 0000 h | Enable CE 3                                      |

| 4A h | 20 h | LSW of Local Address<br>Space 3 Local Base Address<br>(Remap)                | LAS3BA[15:0]   | 0001 h |                                                  |

| 4C h | 26 h | MSW of Expansion ROM<br>Local Base Address<br>(Remap)                        | EROMBA[31:16]  | 0001 h | Disable                                          |

| 4E h | 24 h | LSW of Expansion ROM<br>Local<br>Base Address (Remap)<br>EROMBA[15:0] 0000 h | EROMBA[15:0]   | 0000 h |                                                  |

| 50 h | 2A h | MSW of Local Address<br>Space 0 Bus Region<br>Descriptor                     | LAS0BRD[31:16] | 0081 h | Enable 32Bit<br>Local Bus Width<br>Not ready     |

| 52 h | 28 h | LSW of Local Address<br>Space 0<br>Bus Region Descriptor                     | LAS0BRD[15:0]  | A0C0 h | NRAD 3<br>NWAD 3<br>NXDA 1                       |

| 54 h | 2E h | MSW of Local Address<br>Space 1<br>Bus Region Descriptor                     | LAS1BRD[31:16] | 0000 h | Default value<br>8 Bit Local Bus<br>Width,       |

| 56 h | 2C h | LSW of Local Address<br>Space 1<br>Bus Region Descriptor                     | LAS1BRD[15:0]  | 0000 h | NXDA,<br>NWAD 0,                                 |

# **Design and Function**

| 58 h | 32 h | MSW of Local Address<br>Space 2<br>Bus Region Descriptor | LAS2BRD[31:16] | 0000 h | default value<br>8 Bit Local Bus             |

|------|------|----------------------------------------------------------|----------------|--------|----------------------------------------------|

| 5A h | 30 h | LSW of Local Address<br>Space 2<br>Bus Region Descriptor | LAS2BRD[15:0]  | 0000h  | Width,<br>NXDA,0<br>NWAD 0,                  |

| 5C h | 36 h | MSW of Local Address<br>Space 3<br>Bus Region Descriptor | LAS2BRD[31:16] | 0014 h | 8 Bit Local Bus<br>Width, no ready<br>NRAD 8 |

| 5E h | 34 h | LSW of Local Address<br>Space 3<br>Bus Region Descriptor | LAS2BRD[15:0]  | 2200 h | NRDD 0,<br>NWAD 8,<br>NXDA 1                 |

| 60 h | 3A h | MSW of Expansion Rom<br>Region<br>Descriptor             | EROMBRD[31:16] | 0000 h |                                              |

| 62 h | 38 h | LSW of Expansion Rom<br>Region<br>Descriptor             | EROMBRD[15:0]  | 0000 h |                                              |

| 64 h | 3E h | MSW of Chip Select 0 Base<br>Address                     | CS0BASE[31:16] | 0000 h | CS0 enabled<br>ADD=0XXXh                     |

| 66 h | 3C h | LSW of Chip Select 0 Base<br>Address                     | CS0BASE[15:0]  | 0801 h | Range 2KB<br>FPGA Device<br>Codes            |

| 68 h | 42 h | MSW of Chip Select 1 Base<br>Address                     | CS1BASE[31:16] | 0000 h | CS1 disabled                                 |

| 6A h | 40 h | LSW of Chip Select 1 Base<br>Address                     | CS1BASE[15:0]  | 0000 h |                                              |

| 6C h | 46 h | MSW of Chip Select 2 Base<br>Address                     | CS2BASE[31:16] | 0000 h | CS2 disabled                                 |

| 6E h | 44 h | LSW of Chip Select 2 Base<br>Address                     | CS2BASE[15:0]  | 0000 h |                                              |

| 70 h | 4A h | MSW of Chip Select 3 Base<br>Address                     | CS3BASE[31:16] | 0001 h | CS3 enabled<br>ADD=1XXXXh                    |

| 72 h | 48 h | LSW of Chip Select 3 Base<br>Address                     | CS3BASE[15:0]  | 8001 h | Range 64KB<br>BIS FLASH                      |

| 74 h | 4E h | Serial EEOROM Write–Pro-<br>tected<br>Address Boundary   | PROT_AREA[7:0] | 0030 h | Default                                      |

| 76 h | 4C h | LSW of Interrupt Control/<br>Status                      | INTCSR[15:0]   | 0041 h | Local Int.1 low<br>level                     |

| 78 h | 52 h | MSW of PCI Target<br>Response, Serial EEPROM,<br>Initialization Control | CNTRL [31:15]                              | 1078 h |                                               |

|------|------|-------------------------------------------------------------------------|--------------------------------------------|--------|-----------------------------------------------|

| 7A h | 50 h | LSW of PCI Target<br>Response, Serial EEPROM,<br>Initialization Control | CNTRL [15:0]                               | 0000 h |                                               |

| 7C h | 56 h | MSW of General Purpose I/<br>O Control                                  | GPIOC [31:15]                              | 0049 h |                                               |

| 7E h | 54 h | LSW of General Purpose I/O<br>Control                                   | GPIOC [15:0]                               | 6E30 h | CS2 & CS3<br>enabled GPIO 4<br>used as output |

| 80 h | 72 h | MSW of Hidden 1 Power<br>Management<br>Data Select                      | PMDATA[7:0]                                | 0000 h |                                               |

| 82 h | 70 h | LSW of Hidden 1 Power<br>Management<br>Data Select                      | PMDATA[7:0                                 | 0000 h |                                               |

| 84 h | 76 h | 84 h 76 h<br>MSW of Hidden 2 Power<br>Management<br>Data Scale Reserved | Reserved                                   |        |                                               |

| 86 h | 74 h | LSW of Hidden 2 Power<br>Management<br>Data Scale                       | PMCSR[14:13]<br>hidden,<br>PMCSR[7:0] used | 0000 h |                                               |

Table 5.1 Contents of the PCI9030 Serial Configuration EEPROM

#### 5.4.3 BIS Flash Prom at the Local Bus

This Flash Prom is used to store the BIS information of the unit and is configured via the IPSO Service WEB Tool. The flash prom, connected to PCI bus over the PLX controller, is accessible in the local CS3 address space.

Bus width: 2 byte, data bit 7...0 connected, data bit 15...8 unused;

Corresponding in a double used address range:

Bus cycle length circa 120 nsec for write and 240 nsec for read cycles.

#### Example BIS of a FRED

\$Bis, 1, 20100803, 65536, LVDSMANIP, 1# \$Prd, H122608, 02, 00,, B-NMR-DE, 20100823# \$Nam, FRED Frequency Deputy# \$BasicBoard, 1.0, H12607, 02, 00, FRED Board# \$EndBis, CS1, CS2#

Figure 5.4 Logical Block Diagram of One Channel

| Acronyms  | Local<br>Address      | Function                                                                                                                    | Mode R/W | Bit    |

|-----------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|----------|--------|

| SFRAM     | X0000000-<br>X00000FF | Frequency offset RAM buffer for synchronous update.                                                                         | R/W      | 31- 0  |

| SPHRAM    | X0000100-<br>X00001FF | Phase offset RAM buffer for synchronous update.                                                                             | R/W      | 31- 0  |

| AFRREG    | X0000200              | Asynchronous frequency register.                                                                                            | R/W      | 31- 0  |

| APHREG    | X0000204              | Asynchronous phase register.                                                                                                | R/W      | 31- 0  |

| SCF_A     | X0000208              | Scale factor for channel A.                                                                                                 | R/W      | 31- 0  |

| SCF_B     | X000020C              | Scale factor for channel B.                                                                                                 | R/W      | 31- 0  |

| SCF_C     | X0000210              | Scale factor for channel C.                                                                                                 | R/W      | 31- 0  |

| SCF_DPP   | X0000214              | Scale factor for DPP B0 channel.                                                                                            | R/W      | 31- 0  |

| B0_DEL    | X00000218             | Value of delayed B0 input data.                                                                                             | R        | 19 - 0 |

| DEL_REG   | X0000021C             | Register to delay the B0 Input (delay = register value X NV clock cycles).                                                  | R/W      | 9 - 0  |

| SELRAM    | X00000220             | Signal to select the synchron frequency/phase offset list (RAM buffer select) for write access.<br>Bit0=0 buffer 1 selected | W        | Bit 0  |

|           |                       | Bit0=1 buffer 2 is selected                                                                                                 |          |        |

|           |                       | Read value via DEL_REG                                                                                                      |          |        |

| SELCREG   | X00000224             | Synchronous frequency/phase RAM address counter.                                                                            | W        | 5-0    |

|           |                       | Read value via DEL_REG                                                                                                      |          |        |

| FRPH_UPD  | X00000228             | Update synchronous frequency/phase value via PCI access.                                                                    | W        | х      |

| FREQOFF_A | X00000300             | Read frequency offset of channel A.                                                                                         | R        | 31-0   |

| FREQOFF_B | X00000304             | Read frequency offset of channel B.                                                                                         | R        | 31-0   |

| FREQOFF_C | X00000308             | Read frequency offset of channel C.                                                                                         | R        | 31-0   |

| PHOFF_A   | X0000030C             | Read phase offset of channel A.                                                                                             | R        | 31-0   |

| PHOFF_B   | X00000310             | Read phase offset of channel B.                                                                                             | R        | 31-0   |

| PHOFF_C   | X00000314             | Read phase offset of channel C.                                                                                             | R        | 31-0   |

| INTRPT    | X00000318             | Interrupt and status register & FPGA version register.                                                                      | R/W      | 3 - 0  |

| CLR_ADDC  | X0000031C             | Clear RAM address counter.                                                                                                  | W        | 0      |

| RESET     | X00000320             | Reset device.                                                                                                               | W        | 0      |

Table 5.2 Control Registers and Device Code Commands on FRED

## 5.5 Register and Device Code Description

| Acronyms | Local<br>Address      | Function                                            | Mode R/<br>W | Bit  |

|----------|-----------------------|-----------------------------------------------------|--------------|------|

| SFRAM    | X0000000-<br>X00000FF | Frequency offset RAM buffer for synchronous update. | R/W          | 31-0 |

Table 5.3 Synchronous Frequency Offset RAM

The RT-client can access the Synchronous Frequency Offset RAM (size =  $64 \times 32$  bit) via the PCI bus. The RAM is realized as a dual port memory with two RAM arrays each  $64 \times 32$  bit. In this way the RT-client can preload a new list of offset values while the active list in the second RAM array is in use. The activation of the list is controlled by the RT-client with the SELRAM command. The usable (length) size of the RAM can be defined by the RT-client using the SELCREG (select counter register) command. After a synchronous update command from the DPP, the counter of the frequency RAM buffer is incremented automatically for the next value in the activated list. If the counter reaches the programmed end of the list it is reloaded and points to the first entry again.

The offset value is activated synchronously with the pulse program using a special LVDS UPDATE command from the DPP, and becomes valid with the next NV-clock signal from the DPP. The time between the UPDATE and the NV\_CLOCK should be 100 ns (62.5 ns).

The synchronous frequency offset is a 32 bit signed integer value with a resolution of 0.0047  $\mbox{Hz}$

| Acronyms | Local<br>Address      | Function                                        | Mode R/<br>W | Bit  |

|----------|-----------------------|-------------------------------------------------|--------------|------|

| SPHRAM   | X0000100-<br>X00001FF | Phase offset RAM buffer for synchronous update. | R/W          | 31-0 |

Table 5.4 Synchronous Phase Offset RAM

The functionality of the Synchronous Phase Offset RAM buffer is the same as the frequency offset buffer. The RT-client can access this RAM (size =  $64 \times 32$  bit) via the PCI Bus. The RAM is realized as a dual port memory with two RAM arrays each  $64 \times 32$  bits. In this way the RT-client can preload a new list of offset values while the active list in the second RAM array is in use. The activation of the list is controlled by the RT-client with the SELRAM command.

The offset value is activated synchronously with the pulse program using a special UPDATE command from the DPP and becomes valid with the next NV-clock from the DPP. The time between the UPDATE and the NV\_CLOCK should at least be 100 ns (62.5 ns).

The synchronous phase offset is a 32 bit signed integer fixed point (16.16) value, where 1.0 corresponds to a phase value of 2P.

| Acronyms | Local<br>Address | Function                                | Mode R/W | Bit  |

|----------|------------------|-----------------------------------------|----------|------|

| AFRREG   | X0000200         | Asynchronous frequency offset register. | R/W      | 31-0 |

Table 5.5 Asynchronous Frequency Offset Register

The Asynchronous Frequency Offset Register is a 32 bit (signed integer value) register which can be accessed over the PCI bus. This offset value always becomes active and is sent to the connected SGU's with the next NV\_clock from the DPP. The time delay from the NV\_clock to the data send over the LVDS is 125 ns.

| Acronyms | Local<br>Address | Function                     | Mode R/W | Bit  |

|----------|------------------|------------------------------|----------|------|

| APHREG   | X0000204         | Asynchronous phase register. | R/W      | 31-0 |

Table 5.6 Asynchronous Phase Offset Register

The Asynchronous Phase Offset Register is a 32-bit (signed integer fixed point value 16.16, whereby 1.0 equals to 2PI) register which can be accessed over the PCI bus. The asynchronous phase offset value always becomes active and is sent to the connected SGU's on the next NV\_clock from the DPP. The time from the NV\_clock to the data send over the LVDS is 125 ns.

| Acronyms | Local<br>Address | Function                    | Mode R/W | Bit  |

|----------|------------------|-----------------------------|----------|------|

| SCF_A    | X0000208         | Scale factor for channel A. | R/W      | 31-0 |

| SCF_B    | X000020C         | Scale factor for channel B. | R/W      | 31-0 |

| SCF_C    | X0000210         | Scale factor for channel C. | R/W      | 31-0 |

Table 5.7 Scale Factor Register for Channel A, B, C

The Scale Factor Register is a 32-bit (signed integer value) representing a range from 0..1. The offset values (synchronous and asynchronous) of each channel are summed together and then multiplied with the scale factor. There are three scale factor registers (SCF\_A, SCF\_B, SCF\_C) to adjust the frequency and phase offset of each channel. A scale factor with a value of 0 disables the corresponding channel, meaning that an incoming B0 offset or an synchronous/asynchronous offset value is not transferred to the connected SGU.

| Acronyms | Local<br>Address | Function                         | Mode R/W | Bit  |

|----------|------------------|----------------------------------|----------|------|

| SCF_DPP  | X0000214         | Scale factor for DPP B0 channel. | R/W      | 31-0 |

Table 5.8 Scale Factor Register for the BO Offset

The B0 offset values coming from the DPP has a resolution of 20 bits. The scale factor SCF\_DPP is an unsigned fixed point value with 32 bits. The bits 0-19 are fractional and the bits 20-31 are integer values. In order to adapt the 34-bit frequency range of the SGU, the bits 20-31 of the scale factor are used to shift the 20-bit B0 value in an appropriate manner.

| Acronyms | Local<br>Address | Function                                                                   | Mode R/W | Bit   |

|----------|------------------|----------------------------------------------------------------------------|----------|-------|

| DEL_REG  | X0000021C        | Register to delay the B0 input (delay = register value X NV clock cycles). | R/W      | 9 - 0 |

| Bits   | 3125   | 24            | 23, 22 | 2116                      | 1510   | 90             |

|--------|--------|---------------|--------|---------------------------|--------|----------------|

| Fields | Unused | SELRAM<br>Bit | Unused | RAM Address size counter. | Unused | Delay<br>value |

Table 5.9 Duration Register to Delay the Incoming B0 Value

The B0 offset values coming from the DPP device needs to be delayed in order to synchronize the activation of the frequency offset with the gradient and shim channels. The Duration Register is used to delay the incoming B0 value from the DPP in steps (resolution) of the NV clock. In case of an 1 $\mu$ s NV\_Clock period the delay is programmable from 1 $\mu$ s to 1024 $\mu$ s. The register provides additional bits written by other device codes to read back for test purposes, see table above.

| Acronyms | Local<br>Address | Function                        | Mode R/W | Bit    |

|----------|------------------|---------------------------------|----------|--------|

| B0_DEL   | X00000218        | Value of delayed B0 input data. | R        | 19 - 0 |

Table 5.10 Device Code to Read the Delayed B0 Value

This is a read only register for debugging purposes. The register provides the delayed B0 data from the DPP input, for the output of the duration logic inside the FPGA.

| Acronyms | Local<br>Address | Function                                                                                                                                                                                                                                       | Mode<br>R/W | Bit   |

|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|

| SELRAM   | X00000220        | Signal to select the synchronous frequency/<br>phase offset list (RAM buffer select) for write<br>access.<br>Bit0=0 Buffer 1 can be written, Buffer2 is active<br>Bit0=1 Buffer 2 can be written, Buffer1 is active<br>Read value via DEL_REG. | W           | Bit 0 |

Table 5.11 Select Frequency/Phase RAM List for Synchronous Update

This device code is used to activate the preloaded RAM list to update the synchronous frequency and phase offset. A new frequency/phase value is transferred only if the synchronous UPDATE command (LVDS) from the DPP, or the FRPH\_UP device code via PCI Bus, is detected. The RAM is organized as a dual port buffer including two lists. While one list is always active the other can be written by the RT-client over the PCI bus. The RT-client should load the list before the start of the experiment.

| Acronyms | Local<br>Address | Function                                                             | Mode R/W | Bit   |

|----------|------------------|----------------------------------------------------------------------|----------|-------|

| SECREG   | X00000224        | Defines the size of the synchronous fre-<br>quency/phase RAM buffer. | w        | 5 - 0 |

Table 5.12 Frequency/Phase RAM Buffer Size

This register is used to configure the size of the synchronous frequency/phase offset RAM buffer (e.g. a value of 0 equal a list of 1 frequency/phase offset value, a value of 3 equals a list of 4 entries).

The size is adjustable from 1 to 64 words (HEX value 0-4F). After power-up or reset the register is set to zero. For details see the SFRAM device code description. The value is readable via the DEL\_REG register.

| Acronyms | Local<br>Address | Function                                                  | Mode<br>R/W | Bit |

|----------|------------------|-----------------------------------------------------------|-------------|-----|

| FRPH_UPD | X00000228        | Update synchronous frequency/ phase value via PCI access. | W           | Х   |

Table 5.13 Frequency/Phase Update Command via PCIe

This device code is used to activate a frequency/phase value stored in the synchronous offset RAM buffer via an access from the PCI bus. This mode of operation is only used for initialization or test purposes. The device code simulates the function of the synchronous update command normally sent by the DPP pulse program via the LVDS channel.

| Acronyms  | Local<br>Address | Function                            | Mode R/W | Bit  |

|-----------|------------------|-------------------------------------|----------|------|

| FREQOFF_A | X00000300        | Read frequency offset of channel A. | R        | 31-0 |

| FREQOFF_B | X00000304        | Read frequency offset of channel B. | R        | 31-0 |

| FREQOFF_C | X00000308        | Read frequency offset of channel C. | R        | 31-0 |

Table 5.14 Read Calculated Frequency Offset of Each Channel

These registers are read only and provide the calculated frequency offset for the channel A, B, and C for test purposes.

The B0 offset values coming from the DPP are multiplied with SCF\_DPP and then added to the sum of the valid synchronous and asynchronous frequency offset values from the RT-client. This result is multiplied with the corresponding scaling factor SCF\_i (value range 0..1) for each frequency channel.

#### Foffset,i = SCF\_i\*(B0\_dpp\*SCF\_dpp +Foffset\_sync+Foffset\_async)

| Acronyms | Local<br>Address | Function                        | Mode<br>R/W | Bit  |

|----------|------------------|---------------------------------|-------------|------|

| PHOFF_A  | X0000030C        | read Phase Offset of channel A. | R           | 31-0 |

| PHOFF_B  | X00000310        | read Phase Offset of channel B. | R           | 31-0 |

| PHOFF_C  | X00000314        | read Phase Offset of channel C. | R           | 31-0 |

Equation 5.1: Formula to Compute the Frequency Offset.

Table 5.15 Read Calculated Phase Offset of Each Channel

These registers are read only and provide the calculated phase offset for the channel A, B, and C for test purposes.

The valid synchronous and asynchronous phase offset values from the RT-client are summed up and then multiplied with the corresponding scaling factor SCF\_i (value range 0..1) for each channel. Only the lower bits 15..0 are valid, the bits 31..17 are set to zero. The 360 degree module of the result value is then transferred to the phase offset register of the connected SGU's.

#### PHoffset,i = SCF\_i\*(Phoffset\_sync+Phoffset\_async)

Equation 5.2: Formula to Compute the Phase Offset.

| Acronyms | Local Address                                                               | Function                  | Mode R/W    | Bit                               |

|----------|-----------------------------------------------------------------------------|---------------------------|-------------|-----------------------------------|

| INTRPT   | X00000318         Interrupt and status register &<br>FPGA version register. |                           | R/W         | 3 - 0                             |

| Bits     | 3124                                                                        | 2316                      | 74          | 30                                |

| Fields   | Board Revision.<br>(read only)                                              | FPGA Version (read only). | PERR Status | Interrupt<br>Enable<br>Bits (R/W) |

Table 5.16 Interrupt Status Register

Each bit (0..3) is used to enable (set to 1) or disable/clear (set to 0) the corresponding bit 4..7 as the interrupt source. An initiated interrupt will stay active on the PCI bus until the corresponding register is cleared (set to 0) by the PCI bus master in an appropriate interrupt service routine.

After a reset or power-up the bits are zero and the interrupts are cleared and disabled.

The interrupt/status bit 7..4 indicates that a parity error has occurred on the receiving channel.

- Bit 4 = 1 represent a parity error on input channel A.

- Bit 5 = 1 represent a parity error on input channel B.

- Bit 6 = 1 represent a parity error on input channel C.

- Bit 7 = 1 represent a parity error on input channel B0.

- Bit 23:16 represent the actual FPGA program version number default = 00.

Bit 31:24 board revision number default = 00.

| Acronyms | Local<br>Address | Function                   | Mode R/W | Bit |

|----------|------------------|----------------------------|----------|-----|

| CLR_ADDC | X0000031C        | Clear RAM address counter. | W        | 0   |

Table 5.17 Device Code Clear RAM Address Counter

The device code clears (set to 0) the address counter which points to the active list of the synchron phase and frequency RAM.

| Acronyms | Local<br>Address | Function      | Mode R/W | Bit |

|----------|------------------|---------------|----------|-----|

| RESET    | X00000320        | Reset Device. | W        | 0   |

Table 5.18 Reset Device Code

The device code initialize all the internal register of the FPGA. The SCF\_i, the asynchronous frequency offset register, the delay register and the interrupt status register are set to zero.

The delay register is set to 0. The address and size of the counter which controls the synchronous offset RAM is set to 0. This initialization is also executed during the power-on sequence.

## 5.6 LVDS Word Structure

| Bits   | 47  | 46  | 45  | 44  | 43 | 42 | 41 |       | 32 | 31 |        | 16 | 15 |         | 0  |    |  |

|--------|-----|-----|-----|-----|----|----|----|-------|----|----|--------|----|----|---------|----|----|--|

| Field  | PAR | SYN | WID | PLS | PA | A  |    | REG90 |    | Ρ  | HASE15 | 0  | SI | HAPE15. | .0 |    |  |

| Number | 1   | 1   | 1   |     | 3  |    |    | 10    |    | 10 |        |    | 16 |         |    | 16 |  |

Table 5.19 Word A of LVDS Interface FCTRL to SGU

| Bits   | 47      | 46      | 45      | 44 | 43      | 42  | 41 | 40         | 39 | 38     | 37 | 36   | 35 | 34              | 33  |          | 0   |

|--------|---------|---------|---------|----|---------|-----|----|------------|----|--------|----|------|----|-----------------|-----|----------|-----|

| Field  | PA<br>R | SY<br>N | WI<br>D | NC | O_SEL(2 | 20) |    | _VAL<br>0) | F_ | _VAL(2 | 0) | PH_V |    | SH<br>_VA<br>_L | F_C | DATA (33 | 30) |

| Number | 1       | 1       | 1       |    | 3       |     | 2  |            |    | 3      |    | 2    | 2  | 1               |     | 34       |     |

Table 5.20 Word B of LVDS Interface FCTRL to SGU

| Field      | Value | Description                           |

|------------|-------|---------------------------------------|

| F_DATA 330 |       | 34 bit frequency information.         |

| SHAPE 150  |       | 16 bit amplitude information.         |

| PHASE 150  |       | 16 bit phase information.             |

| REG 90     |       | 10 bit register data.                 |

| PLS, PA, A |       | 3 bit gate information.               |

| SH_VAL     |       | 1 valid bit of amplitude information. |

| PH_VAL 1:0 |       | 2 valid bit of phase information.     |

| F_VAL 2:0  |       | 3 valid bit of frequency.             |

Table 5.21 Bit Fields of the F-Controller Output Word

| REG_VAL 10   |   | 2 valid bit of register data.                                            |

|--------------|---|--------------------------------------------------------------------------|

| NCO_SEL 20   |   | 3 select bits.                                                           |

| WORD_ID(WID) |   | Bit 46 in each word.                                                     |

|              | 0 | Word A.                                                                  |

|              | 1 | Word B.                                                                  |

| SYNCHRO      |   | Reflects the current state of the 20-MHz reference clock at transmitter. |

| PARITY       |   | The even parity bit, created from bit 0 to 45.                           |

Table 5.21 Bit Fields of the F-Controller Output Word

The FRED always transfers a frame A/B word from the connected IPSO FCTRL to the corresponding SGU. A new calculated frequency and phase offset value is embedded in the FCTRL LVDS data stream by the FRED if a time window of 25 ns exists. The  $F_VAL(2..0)$  field in word B is used by the FRED logic to address the new frequency and phase offset register at the SGU unit (Global Frequency and Phase Address = 0 x 5).

| Bits   | 47     | 4637   | 3617     | 165 | 43  | 2    | 1    | 0   |

|--------|--------|--------|----------|-----|-----|------|------|-----|

| Field  | Parity | ADD 90 | Data 190 | GND | RES | LAST | BSTR | NGO |

| Number | 1      | 10     | 20       | 12  | 2   | 1    | 1    | 1   |

Table 5.22 LVDS Word DPP to FRED

| Field  | Bit  | Description                                                                 |

|--------|------|-----------------------------------------------------------------------------|

| Parity | 47   | Even parity of the LVDS word created from bit 0 to 46.                      |

| ADD    | 4637 | 10 Bit address of gradient data word.                                       |

| DATA   | 20   | 20 bit gradient data.                                                       |

| GND    | 12   | Unused connected to GND.                                                    |

| RESERV | 2    | 2 reserve blts.                                                             |

| LAST   | 1    | Indicates the last frame of a gradient data block (active low).             |

| BSTR   | 1    | Indicates the validity of the gradient address and data lines (active low). |

| NGO    | 1    | Indicates that the preloadet gradient data should be activated.             |

Table 5.23 Description of the LVDS Gradient Word from the DPP or GCTRL