Bruker BioSpin

# AVANCE III •

IPSO 19" External Unit Technical Manual

Version 001

think forward

NMR Spectroscopy

The information in this manual may be altered without notice.

BRUKER BIOSPIN accepts no responsibility for actions taken as a result of use of this manual. BRUKER BIOSPIN accepts no liability for any mistakes contained in the manual, leading to coincidental damage, whether during installation or operation of the instrument. Unauthorized reproduction of manual contents, without written permission from the publishers, or translation into another language, either in full or in part, is forbidden.

This manual was written by

Your Name

#### © February 24, 2008: Bruker Biospin GmbH

Rheinstetten, Germany

#### P/N: Z31842 DWG-Nr.: Z4D10607 - 001

For further technical assistance on the AVANCE III unit, please do not hesitate to contact your nearest BRUKER dealer or contact us directly at:

> BRUKER BioSpin GMBH am Silberstreifen D-76287 Rheinstetten Germany

Phone:

+ 49 721 5161 0

FAX:

+ 49 721 5171 01

Email:

service@bruker.de

Internet:

www.bruker.com

i

| Terms and Abbreviations                                    | х     |

|------------------------------------------------------------|-------|

| Important Safety Instructions                              | xiii  |

| Technical Specifications                                   | xiv   |

| Preparation and Transportation                             | xv    |

| Operating Instructions                                     | xvi   |

| Customer Replaceable Units (CRUs)                          | xvii  |

| Service Requests                                           | xviii |

| Intelligent Pulse Sequenz Organizer (IPSO)                 | 1     |

| 1. Condensed Introduction to the Essentials                | 1     |

| 1. 1. Structure and Features                               | 1     |

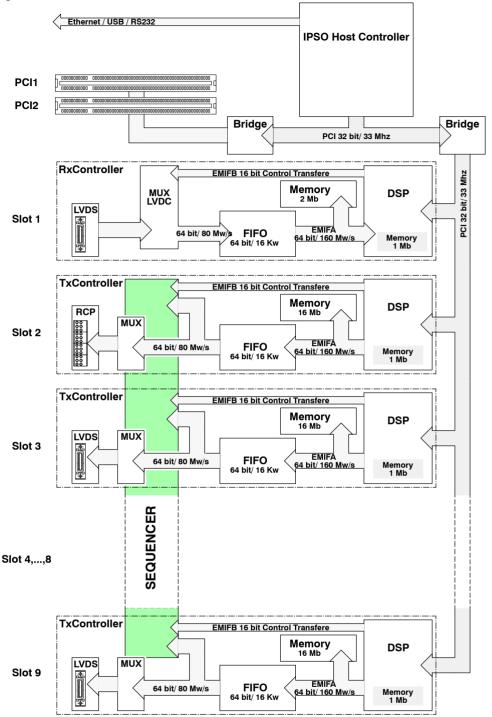

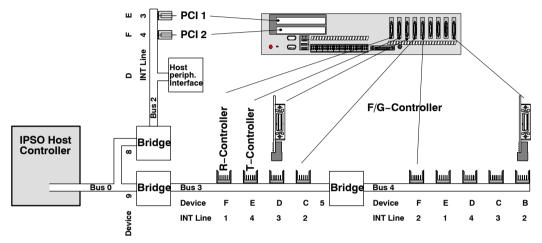

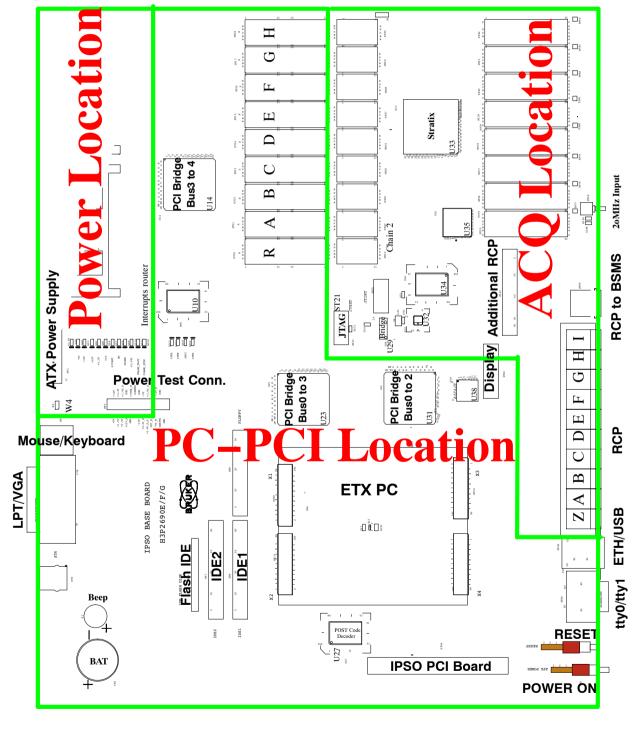

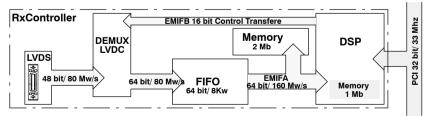

| Figure1: Block diagram of the IPSO 19" Unit                | 4     |

| 1. 2. Handling                                             | 4     |

| 1. 3. Ports                                                | 6     |

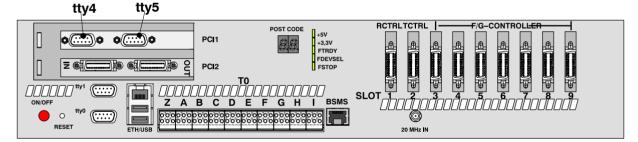

| Figure2: Front View of IPSO 19" Unit                       | 6     |

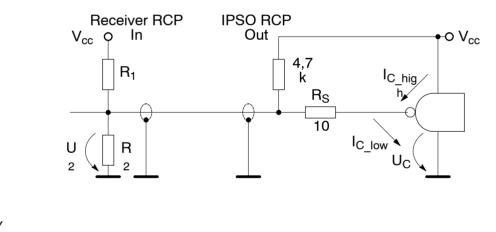

| Figure3: RCP Circuit                                       | 7     |

| Table1: RCP voltage levels and currents                    | 7     |

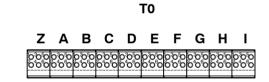

| Figure4: RCP pin location of IPSO 19" Unit                 | 8     |

| Table2: Pin assignment of the RCP signals on IPSO 19" Unit | 8     |

| 1. 4. Boot Operation                                       | 12    |

| Table3: BIOS adjustments                                   | 15    |

| 1. 5. System Configuration                                 | 15    |

| Table4: Interrupt distribution of the IPSO 19" Unit        | 16    |

| Table5: IPSO Versions                                      | 17    |

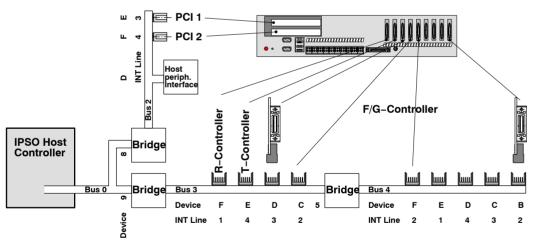

| Figure5: Host bus of the IPSO 19" Unit                     | 17    |

| 1. 6. Power Supply                                         | 18    |

| 2. IPSO Org                                                | 20    |

| 2. 1. Parts and Assemblies of the IPSO 19" Unit            | 20    |

| 2. 2. LVDS Parts                                           | 21    |

| 2. 3. Test Accessories                                     | 21    |

| 2. 4. Introduction Status                                  | 21    |

| 2. 5. History of the IPSO 19" Unit                         | 23    |

| 3. IPSO Host                                               | 25    |

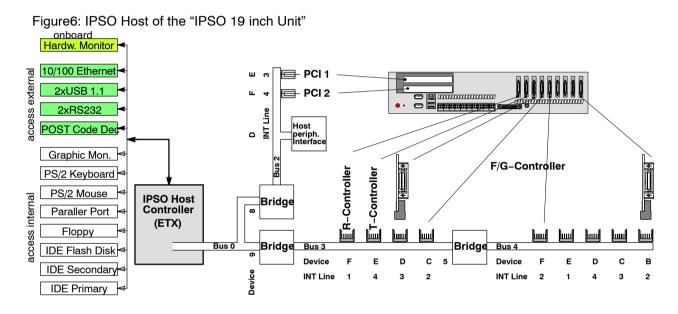

| Figure6: IPSO Host of the "IPSO 19 inch Unit"              | 26    |

| 3. 1. IPSO Host Controller (ETX–Module)                    | 26    |

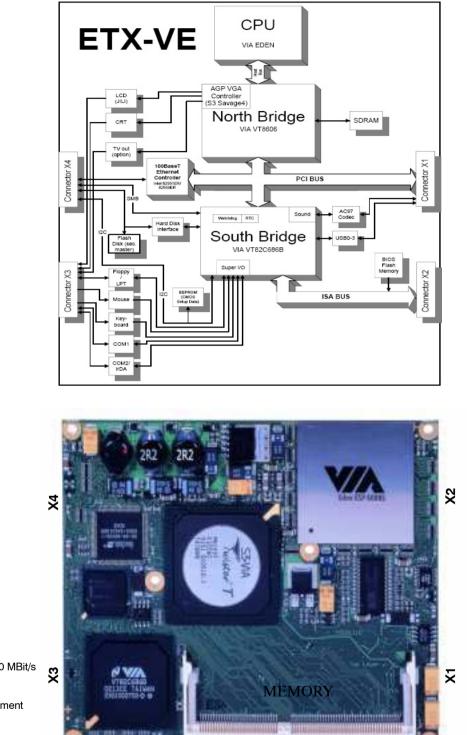

| Figure7: Host Controller "ETX VE4" from Kontron            | 27    |

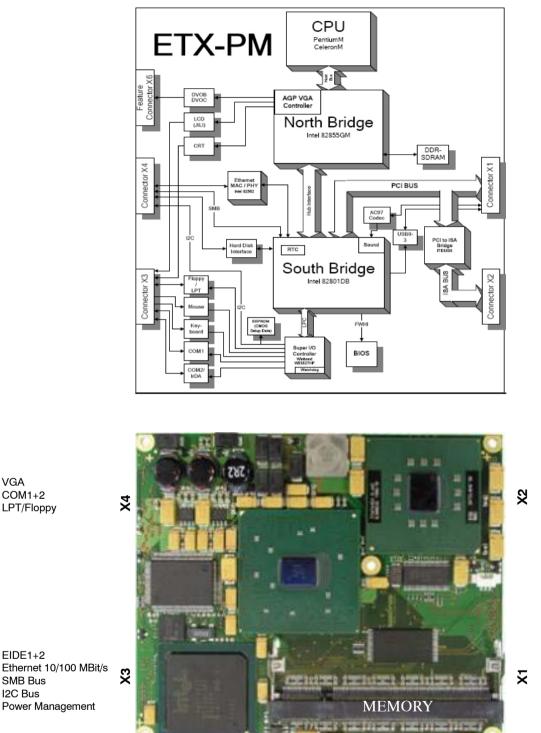

| Figure8: Host Controller "ETX PM" from Kontron             | 28    |

| Table6: Selected Types of ETX-Modules                      | 29    |

| Table7: IPSO Host, predefined ETX requirements             | 29    |

| Table8: BIOS adjustments                                   | 30    |

| 3. 2. PCI Bus                                              | 30    |

ii

| Table9: Voltage level of signals in several bus segments               | 30 |

|------------------------------------------------------------------------|----|

| Figure9: Host bus of the IPSO 19" Unit                                 | 31 |

| Table10: PCI device allocation of special signals in the IPSO 19" Unit | 32 |

| Table11: Signals at the Standard PCI Connector, 32 bit, 5 or 3.3 Volt  | 32 |

| Table12: Pin destinations of signals at the reserved pins of ST10-ST13 | 33 |

| Table13: Pin destinations of signals at the reserved pins of ST14-ST18 | 34 |

| Table14: Pin destinations of signals at the reserved pins of ST44      | 35 |

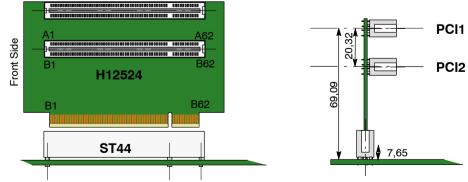

| Figure10: Adapter "IPSO PCI Board", H12524                             | 35 |

| Table15: Access ranges of the DSP C6415                                | 36 |

| Table16: Configuration Space of the "Host Peripheral Interface", PLX   | 37 |

| Table17: Meaning and 4-byte data of the HPI Configuration space        | 37 |

| Table18: PLX Subsystem ID of IPSO devices                              | 37 |

| Table19: IPSO19"/AQS PLX Memory Space Register                         | 37 |

| Table20: IPSO19"/AQS PLX Chip Select Register                          | 38 |

| Table21: IPSO19"/AQS PLX Control Register                              | 38 |

| Table22: IPSO19"/AQS PLX Expansion ROM Register                        | 38 |

| Table23: IPSO hardware configuration register                          | 38 |

| Table24: IPSO Flash Signal description                                 | 39 |

| Figure11: PLX Gen. Purpose I/O Control and JTAG Interface (GPIO: 54h)  | 39 |

| Table25: JTAG signal description                                       | 40 |

| Table26: INTA wiring on "ETX-P1" and IPSO Host of the IPSO-19U         | 40 |

| Table27: INT line assignment                                           | 42 |

| 3. 3. System Management Bus (SMB)                                      | 42 |

| Table28: SMB Device identification – Slave Address                     | 43 |

| Table29: SMB reserved slave Address                                    | 43 |

| Table30: ETX-VE reserved SMB slave address                             | 43 |

| Table31: IPSO reserved SMB slave address                               | 43 |

| Table32: IPSO Winbond SMB first serial slave address                   | 44 |

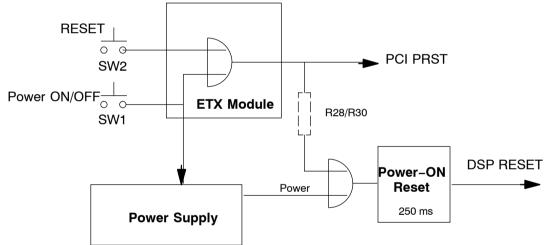

| 3. 4. Reset and Power–ON                                               | 44 |

| Figure12: Effect of Reset Buttons                                      | 44 |

| Table33: Reset Functions                                               | 44 |

| Figure13: Power–On Reset Timing                                        | 45 |

| 3. 5. Engineering Design                                               | 46 |

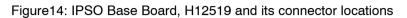

| Figure14: IPSO Base Board, H12519 and its connector locations          | 46 |

| Figure15: Pin count of the JTAG connectors                             | 47 |

| Table34: JTAG pre bridge connect. (19U, H12519 ST21; AQS, H12547 ST20) | 47 |

| Table35: JTAG connect. after bridge (19U H12519 ST21; AQS H12547 ST19) | 47 |

| Table36: IPSO 19" Host, H12519 JTAG structure                          | 47 |

| Table37: Power requirements of IPSO 19" Host, H12519                   | 48 |

| 3. 6. Connectors and Pin Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

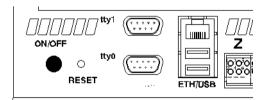

| Figure16: Location of the tty, ETH and USB ports at the IPSO 19inch Unit $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 48 |

| Table38: RS232 signals of ports tty0 and tty1, male                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 48 |

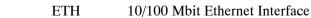

| Table39: Ethernet Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49 |

| Table40: USB Connectors Signal Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49 |

| Table41: Signal Assignment of the Keyboard and Mouse Connectors, female .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49 |

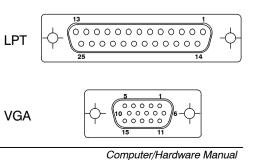

| Figure17: Parallel port and VGA connector, both female                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49 |

| Table42: Pin Assignment of Parallel Port and VGA Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50 |

| Figure18: Pin count of the IDE connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50 |

| Table43: Signal Assignment of IDE Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50 |

| Figure19: ATX Power connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51 |

| Table44: ATX Power Supply Signal Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51 |

| Figure20: Power Test Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51 |

| Table45: Power Test Connector ST5 Signal Assignment (IPSO 19" only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51 |

| 4. Controller IPSO-Tx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 52 |

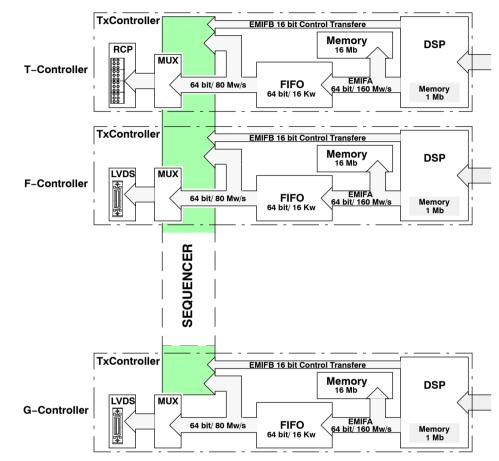

| Figure21: The TxController as T-, F- and G-Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53 |

| 4. 1. Structure of Output Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53 |

| 4. 1. 1. F-Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53 |

| Table46: Word A in the FIFO of F-Controller (64Bit DSP 🕹 FIFO FORMAT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54 |

| Table47: Word B in the FIFO of F-Controller (64Bit DSP 🕹 FIFO FORMAT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 54 |

| Table48: Wort A at LVDS-Interface (Transfer FCTRL to SGU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54 |

| Table49: Wort B at LVDS-Interface (Transfer FCTRL to SGU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54 |

| Table50: Bit Fields of the F–Controller Output Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54 |

| 4. 1. 2. G-Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55 |

| Table51: A-Wort at FIFO output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55 |

| Table52: B-Wort at FIFO output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55 |

| Table53: Gradient Word at LVDS interface, 48 Bit, 80 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 55 |

| Table54: Bit Fields of the G–Controller Words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56 |

| 4. 1. 3. T-Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 56 |

| Table55: FIFO A–Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56 |

| Table56: FIFO B-Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57 |

| Table57: Control Fields of the T-Controller FIFO Words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57 |

| 4. 2. Software Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57 |

| 4. 2. 1. PCI Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57 |

| Table58: Relation between PCI–Addresses and local addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57 |

| 4. 2. 2. Local Address Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57 |

| Table59: Memory Map of the DSP 6415         1.0.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.2         2.3         2.4         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5         2.5 </td <td>57</td> | 57 |

| 4. 2. 3. Content of the DSP Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58 |

| Table60: EMIFA Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58 |

iv

| Table61: EMIFB Configuration Register                                    | 59 |

|--------------------------------------------------------------------------|----|

| Table62: GPIO Configuration Register                                     | 59 |

| 4. 2. 4. Memory at EMIFA                                                 | 60 |

| Table63: Type of external Memories used on the TxControllers             | 60 |

| 4. 2. 5. FIFO at EMIFA                                                   | 60 |

| Table64: Type of FIFOs used on the TxControllers                         | 60 |

| 4. 2. 6. Flash Prom at the EMIFB Bus                                     | 60 |

| Table65: Type of Flash Proms used on the TxControllers                   | 60 |

| 4. 2. 7. Registers at the EMIFB Bus                                      | 61 |

| Table66: Ctrl. Regs. common on F-, G- and T-Controller, EMIFB, space CE0 | 61 |

| Table67: Output Ctrl. Regs. on F- and G-Controller, EMIFB, space CE0     | 61 |

| Table68: RCP Output and Version Reg. on T-Controller, EMIFB, space CE0   | 62 |

| Table69: AQ-Bus Control Registers on T-Controller, EMIFB, space CE1      | 62 |

| 4. 2. 7. 1. Registers of common use on all TxCtrl–Functions              | 62 |

| Table70: Sequencer Flag Register                                         | 63 |

| Table71: Sequenzer & FIFO Status Register                                | 64 |

| Table72: Control of Sequencer RUN/IDLE                                   | 66 |

| Table73: Sequencer Interrupt Control Register                            | 66 |

| Table74: Sequencer Interrupt Status Register                             | 66 |

| Table75: Channel Configuration Register                                  | 67 |

| Table76: Slot-Board-Version Register                                     | 68 |

| 4. 2. 7. 2. Registers used on F–Controller and G–Controller              | 68 |

| Figure22: Bypass Registers goutA, goutB, goutC to LVDS as SGU-A-Word …   | 70 |

| Figure23: Bypass Registers foutD, foutE, foutF to LVDS as SGU-B-Word     | 70 |

| Figure24: Bypass Regs. goutA, goutB, goutC to LVDS, Gradient-Data-Word . | 70 |

| Figure25: Bypass Regs goutA, goutB, goutC to LVDS, Next Gradient Word    | 70 |

| Table77: LVDS Deskew Register                                            | 71 |

| 4. 2. 7. 3. Registers used on T-Controller only                          | 71 |

| Table78: Board Version Register t_brdv                                   | 72 |

| Table79: Register rcpout                                                 | 72 |

| Table80: Relations between tout-registers, FIFO-words and setnmr-words   | 73 |

| Table81: T-Controller Output Register tout0,,tout4                       | 73 |

| Table82: Register rcpout                                                 | 73 |

| Table83: Sequencer Program Version                                       | 73 |

| Table84: Control of AQSTART                                              | 74 |

| Table85: Control of Suspend/Resume                                       | 75 |

| Table86: Register of Suspend Trigger Select                              | 75 |

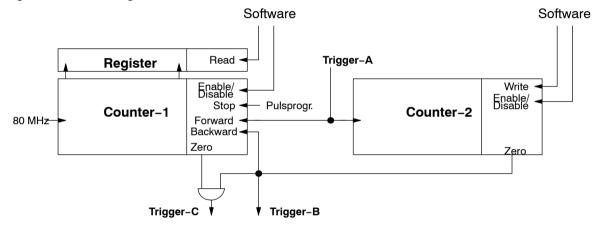

| Figure26: Next-Value Counter                                             | 76 |

| Table87: Function of Emergency Stop                                      | 76 |

| Figure27: Counter logic                                                          | 77 |

|----------------------------------------------------------------------------------|----|

| Table88: Select Reg. for external trigger source of Rotor synchronisation        | 78 |

| Table89: Rotation Counter Enable                                                 | 78 |

| Table90: Rotation Counter-1                                                      | 79 |

| Table91: Rotation Counter-2                                                      | 79 |

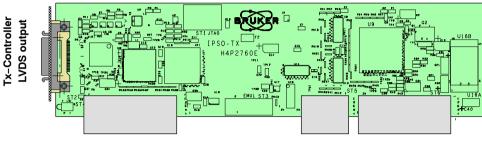

| 4. 3. Engineering Design                                                         | 80 |

| Figure28: TxController Board of the IPSO 19" Unit                                | 80 |

| Table92: JTAG Structure on IPSO TxController Board of the IPSO 19" Unit          | 80 |

| 4. 4. Pin allocation of Connectors                                               | 81 |

| Figure29: Pin location of the 48–Bit LVDS Connector at PCB                       | 81 |

| Table93: Cable and Pin Assignment                                                | 81 |

| 5. RxController                                                                  | 83 |

| Figure30: The RxController                                                       | 83 |

| 5. 1. Structure of input words at the LVDS–Receiver and the FIFO                 | 84 |

| 5. 1. 1. Words from F–Controller                                                 | 84 |

| Table94: F–Ctrl words at output of LVDS receiver and FIFO (F–Ctrl Mode) $\ldots$ | 84 |

| Table95: Bit Fields of the F-Controller Output Word                              | 84 |

| 5. 1. 2. Words from G–Controller                                                 | 84 |

| Table96: G-Ctrl words at output of LVDS receiver and FIFO (G-Ctrl Mode)          | 85 |

| Table97: Bit Fields of the G-Controller Output Word                              | 85 |

| 5. 1. 3. Words from the DRU                                                      | 85 |

| Table98: DRU words at output of LVDS receiver and FIFO (DRU Mode)                | 85 |

| Table99: Bit Fields of the DRU-Controller Output Word                            | 85 |

| 5. 2. Software Interface                                                         | 85 |

| 5. 2. 1. PCI Addresses                                                           | 86 |

| Table100: Relations between PCI- and local addresses on R-Controller             | 86 |

| 5. 2. 2. Local Address Layout                                                    | 86 |

| Table101: Memory Map of the DSP 6415 on R–Controller                             | 86 |

| 5. 2. 3. Content of the DSP Configuration Registers                              | 87 |

| Table102: EMIFA Configuration Register                                           | 87 |

| Table103: EMIFB Configuration Register                                           | 87 |

| Table104: GPIO Configuration Register                                            | 88 |

| 5. 2. 4. Memory at EMIFA, space CE0                                              | 88 |

| Table105: Type of external Memories used on the RxControllers                    | 88 |

| 5. 2. 5. FIFO at EMIFA, space CE3                                                | 88 |

| Table106: Type of FIFOs used on the RxControllers                                | 88 |

| 5. 2. 6. Flash Prom at the EMIFB Bus, space CE2                                  | 89 |

| Table107: Type of Flash Proms used on the RxControllers                          | 89 |

| 5. 2. 7. Registers at the EMIFB Bus, space CE0                                   | 89 |

| Table108: Device Codes on EMIFB (CE0 space), existent on RCtrl                   | 89 |

| 5. 2. 7. 1. Register Description                              | 89 |

|---------------------------------------------------------------|----|

| Table109: Control Register                                    | 90 |

| Table110: Channel Register                                    | 90 |

| Table111: Channel Configuration Register                      | 91 |

| Table112: Slot-Board-Version Register                         | 91 |

| Table113: Status Register                                     | 92 |

| 5. 3. Data Acquisition and Time Measurement                   | 93 |

| 5. 3. 1. R–Ctrl operating in F–Controller Mode                | 93 |

| Table114: Effect of Word–ID in F–Controller Mode              | 93 |

| 5. 3. 2. R–Ctrl operating in G–Controller Mode                | 94 |

| Table115: Effect of Valid and NG bit in G–Controller Mode     | 94 |

| 5. 3. 3. R–Ctrl operating in DRU Mode                         | 94 |

| Table116: Effect of Data and Control bit in DRU Mode          | 94 |

| 5. 4. Engineering Design                                      | 95 |

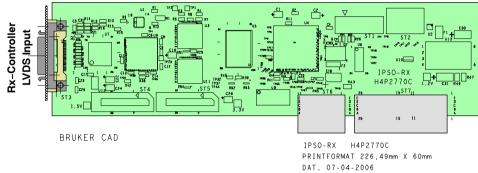

| Figure31: RxController of IPSO 19" Unit                       | 95 |

| Table117: JTAG Structure on RxController of the IPSO 19"-Unit | 95 |

| Table118: Currents                                            | 96 |

| 5. 5. Pin allocation of Connectors                            | 96 |

| Figure32: Pin location of the 48–Bit LVDS Connector at PCB    | 96 |

| Table119: Cable and Pin Assignment                            | 96 |

IPSO 19"

х

# **Terms and Abbreviations**

The following table lists terms and abbreviations used in this dokument.

| TOPSPIN-PC                                                                           | Processing Computer running TOPSPIN; server of the IP-<br>SOs diskless Linux                                                                                                                                                                    |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPSO                                                                                 | Intelligent Pulse Program Organizer;<br>System consisting of the IMB, the PCI-Host and a different<br>bundle of Controllers                                                                                                                     |

| IPSO AQS                                                                             | IPSO version to be mountet in the AQS-Rack ("Nanobay" or<br>"Microbay")                                                                                                                                                                         |

| IPSO 19" Unit,<br>IPSO 19inch Unit                                                   | IPSO version as standalone Case of the 19-Inch Standard                                                                                                                                                                                         |

| IPSO Host,<br>CCU, PCI-Host, spect                                                   | Assemly group containing the IPSO Host Controller (PC module, ETX), Computer Interfaces and the Host Bus (PCI)                                                                                                                                  |

| IPSO Host Controller                                                                 | IBM-PC compatible Modulcomputer (ETX)                                                                                                                                                                                                           |

| IPSO AQS Host                                                                        | IPSO Host of IPSO AQS including computer, interfaces and R-Controller                                                                                                                                                                           |

| IPSO Motherboard, IMB                                                                | IPSO Host of IPSO 19"–Unit including computer, interfaces and bus structure                                                                                                                                                                     |

| IPSO-Tx,<br>TxController,<br>TxCtrl                                                  | TxController, capable of sending sequences of application<br>parameters;<br>Single channel for IPSO 19" Unit,<br>five channel for IPSO AQS                                                                                                      |

| IPSO AQS ACQ                                                                         | Five channel TxController board of IPSO AQS                                                                                                                                                                                                     |

| IPSO-Rx,<br>RxController, RC, rc<br>R-Controller,<br>RxCtrl                          | RxController, capable of receiving sequences of application results or parameter streams sent by TxCtrl in cases of using the "ipsotest"                                                                                                        |

| T-Controller, TC, tc;<br>F-Controller, FC, FC1,<br>fc, fc1;<br>G-Controller, GC, gc; | TxController with dedicated and application specific functio-<br>nallity for:<br>T=Timing control,<br>F=Frequency control,<br>G=Gradient control;<br>In print messages: "F-Controller1, (fc1)" means the first<br>channel frequency controller. |

| X-Controller, XC, xc<br>Controller Board, Con-<br>troller | Collektive term of controllers without functional differentia-<br>tion; means in each case a TC or RC controller based on<br>C6400                                                                                                                      |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U-Controller, UC, uc;                                     | Stands for "unknown controller" and describes a C6400-ba-<br>sed controller with unknown content in its version register,<br>e.g. a C6400-based device of an unknown manufacturer                                                                       |

| C6400                                                     | CPU of the Controller; DSP from Texas Instruments                                                                                                                                                                                                       |

| ІМВ                                                       | IPSO Motherboard, IPSO Host of 19"-Unit                                                                                                                                                                                                                 |

| Host-Bus, PCI-Bus                                         | Control-, data- and addressbus for communication between<br>Host Controller and X-Controllers                                                                                                                                                           |

| RCP                                                       | Real-Time-Clock-Puls                                                                                                                                                                                                                                    |

| LVDS Cable                                                | Transmission cable at the LVDS connector of X-Controllers                                                                                                                                                                                               |

| PCI-Master                                                | PCI device which is able to initiate a transaction over the PCI bus (Host Bus)                                                                                                                                                                          |

| Local Address                                             | Onboard address out of the local processor's address layout, different from the PCI Address in the upper 10 bit                                                                                                                                         |

| PCI Address                                               | Onboard address out of the PCI bus address layout, different from the Local Address in the upper 10 bit;<br>The Bruker user interfaces use the Local Address only.                                                                                      |

| channel, Kanal                                            | Controller dedicated to a subtask of the application                                                                                                                                                                                                    |

| AQ-Bus                                                    | Bundle of signals which control on a clock base (80 MHz) the channel operation and the communication between the channels                                                                                                                               |

| Master Controller                                         | Controller of the zero-delay channel (first one) which deci-<br>des on the AQ-Bus operation and communicates with the<br>Slave Controllers<br>One exclusive master has to be in the system. Only the ma<br>ster drives many of the AQ-Bus signals.      |

| Slave Controller                                          | A controller which is funcional dependent on the decisions of<br>the Master Controller.<br>"Slaves" have a clock cycle delay with respect to the Master<br>of $\stackrel{>}{_{=}}$ 0<br>It is not allowed to have only Slave Controllers in the system. |

2008-02-20

IPSO 19"

| Last Slave Controller                     | Is the Slave with the greatest delay in the system respective<br>to the Master.<br>Only this Slave drives some AQ–Bus signals and communi-<br>cates with the Master.                           |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Independent Controller                    | Whenever started runs its own program independent of the AQ-Bus.<br>The Independend Controller drives no AQ-Bus signals. It is not allowed to have only Independend Controllers in the system. |

| trigger, trigger event,<br>external event | External signal which can assign the time of any decision to the Master Controller                                                                                                             |

| Firmware                                  | Software which is loaded to the controller memory and runs the C6400                                                                                                                           |

| AQ device driver                          | A program that must be loaded into the Linux Kernel which enables access to the X-Controllers                                                                                                  |

| AQSTART                                   | Start of application; carried out via the T–Controller and AQ–<br>Bus                                                                                                                          |

| semif                                     | Register to select FIFO or C6400 to load the LVDS output                                                                                                                                       |

| EDMA, QDMA                                | Transactions of data between memory ranges and/or interfa-<br>ces initiated by the DMA controller of C6400; EDMA=Exten-<br>ded DMA, QDMA=Quick DMA (not faster than EDMA)                      |

| OPT, SRC, CNT, DST,<br>IDX, RLD           | Fields of the DMA controllers:<br>Option, Source, Count, Destination, Index, Reload                                                                                                            |

| EMIFA, EMIFB                              | Interfaces of the C6400 to the memory and registers;<br>EMIFA=64-Bit, EMIFB=16-Bit                                                                                                             |

|                                           |                                                                                                                                                                                                |

IPSO 19"

# **Important Safety Instructions**

This Manual covers the spectrometer control unit called IPSO in versions:

- IPSO 19inch

- which are used in the AVANCE III spectrometers

It is mandatory to read this whole chapter before installation and use !

# **General Safety Instructions**

These instructions refer to any IPSO model.

The IPSO can be damaged by inappropriate usage. The damage could be such, that the equipment must not be used before having been checked by the service.

The user should re-check the equipment at regular intervals for any damage or wear and is expected to inform the service immediately of any abnormality.

Do not use the equipment and inform the service staff, if you are in doubt about the correct state of any component.

In the unlikely case of one of the following, stop using the equipment, interrupt the current supply, disclose this circumstance to the service staff and ask for instructions:

- The power cord, power plug or power supply are cracked, brittle or damaged

- Signs of excessive heat appear

- There is evidence or suspicion that a liquid has intruded into any enclosure

- The power cord or the power supply have been in contact with any liquid

- The IPSO has been dropped or damaged in any way

- The equipment does not work correctly

Some components of IPSO can be installed or replaced by the customer. These components are referred to as "Customer Replaceable Units" (CRUs), see below.

With the exception of the Customer Replaceable Units (CRUs), all servicing must be performed by qualified service personnel.

Before maintenance, repair or shipment, the IPSO must be completely switched off and unplugged or disconnected and dismounted from its rack.

# **Special Safety Symbols**

These symbols are used on the equipment and/or throughout this manual. They alert to danger and important information:

| Warning | This symbol denotes hints or instructions throughout this<br>manual whose noncompliance could lead to erroneous or incal-<br>culable behaviour of the system                                                                                                      |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Danger  | Throughout this manual, the symbol indicates hints or instruc-<br>tions whose noncompliance can lead to an injury of the user or<br>whose necessary compliance implies also a risk.<br>On the equipment, the symbol implies also a danger and alerts<br>the user. |

BRUKER BioSpin

xiv

| Danger | Throughout this manual, this symbol indicates necessary ac-<br>tions which imply a risk of being injured by high voltages.<br>On the equipment, the symbol indicates electrical hazards and<br>alerts the user. |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Danger | On the equipment, the symbol indicates hot surfaces and alerts the user.                                                                                                                                        |

# **Product and Manufacturer**

The following description refers to:

| Product      | IPSO 19inch Unit<br>P/N H9987                                           |

|--------------|-------------------------------------------------------------------------|

| Manufacturer | Bruker BioSpin GmbH<br>Silberstreifen 4<br>76287 Rheinstetten (Germany) |

| Conformity   | EN 61010-1                                                              |

# **Technical Specifications**

# Non-Intended Usage

All IPSO models contain generally available computer assemblies and provide their standard interfaces. All IPSO models are not qualified to be used beyond their "Intended Usage" neither as a single computer nor as networked one.

# **Intended Usage**

All IPSO models are dedicated only for the limited purpose of being used to steer the *AVANCE <sup>III</sup>* spectrometers of the manufacturer.

# **Environmental Requirements**

| Permissible ambient temperature | 5 to 40 degree Celsius                                                                                        |

|---------------------------------|---------------------------------------------------------------------------------------------------------------|

| Permissible altitude            | up to 2000 m (above sea level)                                                                                |

| Relative humidity.              | max 80% up to 31 degree Celsius and linear decreasing to 50% at 40 degree Celsius                             |

| Permissible storage temperature | 5 to 40 degree Celsius                                                                                        |

| Pollution degree                | 2,according to EN 61010–1 or<br>IEC 60664–1<br>any pollution is non–conductive,<br>except condensed moisture. |

| Audible noise                   | < 50 dB                                                                                                       |

|                                 |                                                                                                               |

# Utility Requirements of "IPSO-19inch Unit"

| Ingress protection class | IP 20,                                    |

|--------------------------|-------------------------------------------|

|                          | secured against touching dangerous points |

|                        |                                     | inside,<br>not secured against ingress of water.                                                                       |

|------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Overvoltage protection | on category                         | CAT II, according to EN61010–1or<br>IEC60664–1<br>safe against overvoltage by switching,<br>not safe against lightning |

|                        |                                     | Surge immunity of PSU is level 3, according to IEC61000-4-5                                                            |

| IEC protection class   |                                     | Class I, according the IEC 61140,<br>connected to mains by phase, neutral and<br>protective–earth                      |

| Input Voltage range    | 110V to 240 V $\-$                  |                                                                                                                        |

| Frequency              | 50/60 Hz                            |                                                                                                                        |

| Input Power            | 100 VA                              |                                                                                                                        |

| Fuse on mains input    | 250VAC 6.3A                         |                                                                                                                        |

| Connection             | Socket outlet with according to VDE | n phase, neutral and protective–earth<br>2 0620–1                                                                      |

#### Weight and Dimensions of "IPSO-19inch Unit"

| Weight    | 11 kg                                                             |

|-----------|-------------------------------------------------------------------|

| Dimension | (420x532x85) mm,<br>according to DIN41494 or IEC 297, (84TE, 2HE) |

# **Preparation and Transportation**

Because of the IPSO contains a large amount of sensitive and damageable parts and assemblies, it must be handled with care and must not be dropped.

#### Storage

If the IPSO is not installed immediately, it has to be inspected for any damage during shipment and must be stored in the original packing.

Attention has to be paid to the recommended storage conditions, the temperature and the protection from moisture.

# Unpacking

All packing materials have to be removed. The equipment must be inspected for any damage during shipment.

If damage has occurred during transit, all the shipping cartons should be stored for further investigation. A claim for shipping damage has to be advised immediately.

#### Installation

All the requirements concerning environment described in the Technical Specifications have to be met.

To reduce the risk of electric shock and malfunctioning, install these devices in a temperature– controlled and humidity–controlled indoor area free of conductive contaminants.

The power supply cord is intended to serve as the disconnect device. The socket–outlet should be near the equipment and should be easily accessible.

The installation of IPSO has to meet all instructions of the "User's Guide" and of Chapter "1." of this manual.

Each IPSO model has to be installed in its dedicated rack:

IPSO 19inch Unit: AVANCE CONSOLE WIRED MICROBAY P/N H03128

Make sure that ventilation and space requirements are according to specification. There must be clearance at the rear for ventilation and at the front for operation.

Make sure that cabling can not be a source of danger.

All cables have to be connected before the IPSO is put into operation.

# **Operating Instructions**

The only user operations permitted are:

- Starting up and shutting down the IPSO

- Operating the users software interface

- Connecting data interface cables

- Replacing the Customer Replaceable Units (CRUs)

These operations must be performed according to the instructions in Chapter "1." et seq. of this manual. During any of these operations the user must take the greatest care and perform only the prescribed operations.

Do not operate the equipment in the presence of flammable gases or fumes.

# **Operator Protection**

The electronic circuitry of IPSO is operating with low and safe voltages, except for the power supply and its connection to mains. Nevertheless, any electrical equipment can become a source of danger under extreme conditions.

| Danger | Do not loosen, connect or touch any cable during lightning.                                           |

|--------|-------------------------------------------------------------------------------------------------------|

| Danger | Do not use a cable that shows any signs of damage or that<br>have been stressed and could be damaged. |

Do not open the IPSO enclosure, except for replacing CRUs.

Where opening of the IPSO enclosure is necessary, switch off and let five minutes elapse to let hot spots cool down.

Pay attention to the special Safety Symbols inside.

# **Function Protection**

Handling under ESD safety conditions is absolutely necessary.

| Warning | Don't touch uncovered metal of the PCB, electronic devices<br>and connectors before discharging yourself!                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|

| Warning | Do not connect a receiver to the LVDS connector of the con-<br>troller in Slot2 of the IPSO 19" Unit. There will never be<br>valid data. |

| Warning | A LVDS cable should never be removed from or connected<br>to a powered controller. Corrupted data could be sampled as<br>valid.          |

| Warning | Do not connect more than one Gradient Amplifier to the same system.                                                                      |

# **Customer Replaceable Units (CRUs)**

To insert and remove the Customer Replaceable Units, follow the instructions in Chapter "1." of this manual.

Replacing CRUs requires opening of the enclosure. Before doing this, the unit must be completely switched off and unplugged or disconnected and dismounted from its rack.

In case of IPSO–AQS, the replacement of units should be left to qualified service personnel.

Depending on the IPSO model, there are the following replaceable units:

| IPSO 19inch Unit: | IPSO-TxController Board        | P/N H12538F2        |

|-------------------|--------------------------------|---------------------|

|                   | IPSO-RxController              | P/N H12532          |

|                   | PC 2CH RS232 PCI Adapter       | P/N O10394          |

|                   | PCI RxController               | P/N H12565          |

|                   | DPP1 Digital Preemphasis Board | P/N H12513F1        |

|                   | RTC Battery 3V Lithium         | P/N 72385,          |

|                   |                                | type "Varta CR2032" |

# Maintenance and Cleaning

# Cleaning

Cleaning the surface of the enclosure and/or front panel can be carried out by the customer, if the following instructions are adhered to.

- 1. Switch off the equipment and unplug the power cable and all data cables.

- 2. Clean up the surface with a dry or damp cloth.

**3.** Let the enclosure completely dry before installing

4. Connect all cables and power up.

# Maintenance

Any IPSO model can be expected to have a long and trouble–free life with a minimum of preventive maintenance. Environmental issues are essential in determining the reliability. The temperature and humidity have to be within specifications. The area around should be kept relatively clean and dust free.

With the exception of the Customer Replaceable Units (CRUs), all servicing must be performed by qualified service personnel.

Before maintenance, repair or shipment, the unit must be completely switched off and unplugged or disconnected and dismounted from its rack.

# Service Requests

In case of questions or problems, please contact your nearest Bruker office or representative.

A list of all our offices is published on the web: http://www.bruker-biospin.com/contact\_us.html

BRUKER BioSpin

# Intelligent Pulse Sequenz Organizer (IPSO)

This Manual covers the spectrometer control unit called IPSO in versions:

• IPSO 19inch

which are used in the AVANCE III spectrometers

Chapter "1." summarizes the most essential informations for users to get started quickly and to avoid beginner's mistakes without reading plenty of pages.

Chapter "2." lists the part/order numbers of the main assemblies, subassemblies and devices.

Chapter "3." et seq. provide the more detailed descriptions of assemblies and devices.

# 1. Condensed Introduction to the Essentials

# Do's and Don'ts

- Do not connect a receiver to the LVDS connector of the controller in Slot2 of the IPSO 19" Unit. There will never be valid data.

- A LVDS cable should never be removed from or connected to a powered controller. Corrupted data could be sampled as valid.

- Do not connect more than one Gradient Amplifiers to the same system.

# 1. 1. Structure and Features

# Features

- IPSO is a digital spectrometer control unit with a variable number of output channels (TxControllers)

- Each TxController outputs a stream of 48-bit words at a clock rate of 80 MHz per word

- Transferral of a complete set of frequency parameters requires two words.

- The time resolution of parameter switching in any combination of Frequency, Phase, Amplitude is 12.5 nsec.

- The minimal duration of any combination of parameters is 25 nsec.

- Gradient channels require one word per gradient.

- The maximal number of addresses for different gradients (the max. number of gradient channels) is 1k.

- A constant time delay between the outputs of the different TxControllers may be adjusted to any number of 80MHz clock cycles up to 2<sup>29</sup>x12.5nsec

# Structure

The distinctive Parts of the system are the Host Controller charged with administrative tasks, the number of TxControllers generating and transferring the parameter sequences and the Sequencer providing for a means of communication between the TxControllers.

# **The Controllers**

The system contains the 3 types of controllers, Host Controller, RxController and the TxController.

| Host Controller: | There is only one Host Controller in the system. The Host Controller<br>is an IBM compatible PC with all standard interfaces thus making ac-<br>cess possible to the whole pool of standard hardware and software.<br>The Host Controller boots its operating system software (diskless LI-<br>NUX) from and communicates with the TOPSPIN–PC over Ethernet.<br>It also communicates over its standard interfaces with the Rx– and the<br>TxControllers and with peripheral devices. |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxController:    | The RxController is able to receive 48-bit words at its LVDS interface<br>at a rate of up to 100-Mega words. Therefore it can be used as a fast<br>data link from the receiver channel to the transmit channel, bypassing<br>the ethernet and the TOPSPIN-PC. Furthermore all TxControllers and<br>their LVDS interfaces can be tested with the IPSOTEST if their inter-<br>faces are connected to a RxController.                                                                   |

|                  | Realtime processing of that data can be done by an onboard DSP. The processed data can be transferred by the DMA channels of the DSP over the system bus to any other controller or may be fetched by any other controller.                                                                                                                                                                                                                                                          |

|                  | Usually there is one RxController in the system. Without additional software (that means transparent to the software) it is possible to include additional RxControllers using extension boxes.                                                                                                                                                                                                                                                                                      |

|                  | The RxController has no connections to the Sequencer and communi-<br>cates and exchanges data with other controllers via the system bus. It<br>will function in any slot of the IPSO but should be inserted in slot 1.                                                                                                                                                                                                                                                               |

| TxController:    | Depending on its configuration, the TxController can be used for any<br>of the 3 output functions in the system. These functions are the T–<br>Controller servicing the RCP outputs at T0 with timing signals, the<br>F–Controller generating the frequency parameters for the SGUs and<br>the G–Controller generating the gradient packets for the amplifiers.                                                                                                                      |

|                  | The TxControllers and their common Sequencer are the most decisive<br>parts of the IPSO system. The Sequencer is a single device, just one<br>piece of silicon. It contains the communication and decision making<br>logic of all TxControllers and the communication bus between them<br>known from former systems as the AQ–Bus. The AQ–Bus allows for<br>real time communication on a 1–clock base of 12.5 nsec.                                                                  |

|                  | The controller itself consists of a DSP with memory, FIFO, output<br>logic and interfaces to the system bus and the Sequencer. The DSP<br>gets its code from the Host Controller, generates the parameter se-<br>quences and writes them into the FIFO. Its most important task is to<br>keep the FIFO full. The Sequencer (once started) reads the words out<br>of the FIFOs of all controllers, realizes the defined timing in each<br>channel and controls the outputs.           |

|                  | The global functions of the Sequencer (e.g. START, STOP, SUS-<br>PEND, RESUME and so on) are part of the Sequencer logic of the<br>T-Controller. Therefore a T-Controller has to be in the system to<br>carry out any type of acquisition.                                                                                                                                                                                                                                           |

# LVDS

The LVDS cable is the transport media for digital data words between the Tx- and the RxControllers respectively and the peripheral devices like SGU, Gradient Amplifier, DRU and DPP (Digital Preemphasis Processor). The abbreviation LVDS means "low voltage digital signal". The voltage switching range of the data lines is between 1.0V and 1.4V.

The used devices take 48-bit data words at a clock rate of 80MHz (and 100MHz between DRU and RxController respectively) and serialize and transport them over 8 balanced data line pairs accompanied by one clock pair. At the receiver side the data stream is deserialized and the 48-bit data word and its 80MHz clock are reconstructed.